尊敬的团队:

我的一位客户进行了以下实验:

方法 1:使用 CLB 生成脉冲信号脉冲和方向信号 DIR。 信号通过 GPIO 输出、然后连接到 QEP A/B 引脚、以便能够正常计数。

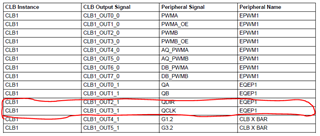

方法 2:QEP 配置在方法1中保持不变、不同之处在于当 QDIR 和 QCLK 在内部连接时、不能对 QEP 进行计数(QPOSCNT 始终为零)。 CLB 和 QEP 之间的接触信号如下:

QDIR 与方法1中的 DIR 波形相同;QCLK 是方法1中脉冲信号下降沿时刻的脉冲、宽度为10ns。 实现方法是通过新的配置语句:Clb1LogicCtrlRegs.clb_out_EN = 3<<10; 这样、QEP 就无法实现计数(QPOSCNT 始终为零)

请帮助分析导致方法2不计数的原因?

此致