主题中讨论的其他器件:MOTORWARE

我正在编写一些代码、以便与使用类似 SPI 的通信的外部外设进行交互。 我给它一个时钟、它给我数据、所以我将使用外设、如下所示:

- 读取 SPI 的 RX FIFO 中的数据

- 处理数据

- 填充 Tx FIFO

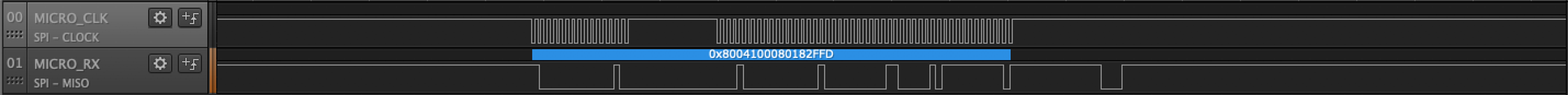

此例程在 SYS-BIOS 中以1kHz 的频率运行。 问题是、我会遇到如下所示的布线:

顶部(CLK)迹线上的间隙导致外设超时、并认为下一个字是一个新的事务。

下面是填充 TX FIFO 的代码:

//填充 FIFO 以准备新样本。 for (int word_need=4;word_need>0;word_need---){ SPI_Handle_->SPITXBUF = 0xFFFF; //等待缓冲区清空 while (SPI_getTxBufferStatus (SPI_Handle_)=SPI_TxBufferStatus_Full); }

这不是原子的、因此当中断时、填充过程可能会延迟。 我要做的是在 SPI_enableTx()之后放置一个 SPI_disableTx(),但出于某种原因,当您禁用 TX 时,它不会停止外设计时,这会破坏这一想法。

希望能在这方面提供一些帮助!

谢谢!