Other Parts Discussed in Thread: ADS1203, ADS1202

主题中讨论的其他器件:ADS1203、 ADS1202

我对 SDFM 有一些相关的问题:

SDFM 过去有一种奇怪的行为。 我将使用该模块来监控电流传感器、以便在发生短路时快速关闭器件。 为此、我使用内部具有低过采样率的比较器单元、并使用具有更高过采样率的 SDFM. Data 进行正常测量。

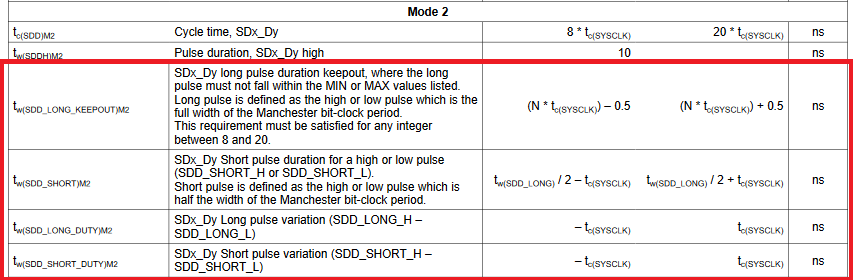

在测量时、我使用具有 Σ-Δ 调制器的独立 PCB。 由于版本不同、我使用不同的 Σ-Δ 调制器(ADS1203、ADS1202、AMC1303E)。 在首次设置期间、我意识到10MHz 调制器不能与 TMS230一起工作、因为它在其 SDMF 中仅支持8...20*t_SYSCLK。 因此、我决定将 TMS 的频率降低至180MHz、因此它还支持10MHz 调制器。

通过使用电路板、我注意到 SDFM 比较器有时毫无理由地跳闸。 这必须是由于 SDFM 同步错误造成的。

为了更深入地了解该问题、我对 FPGA 进行了编程、以输出曼彻斯特编码 Σ-Δ 流并使用参数。 为了查看 SDFM 是否失去同步、我每次有新数据可用时都会设置一个中断。

我觉得有点奇怪。 以精确的200MHz 运行 TMS 只支持9.2到15.4Mhz 的数据流。 除此之外的一切都将触发跳闸。 但将频率更改为190甚至210MHz 将使 SDFM 支持更高的频率。 将引脚的 QSEL 从异步更改为同步有时会改善行为、但并非总是如此。 具体取决于数据流的确切频率。

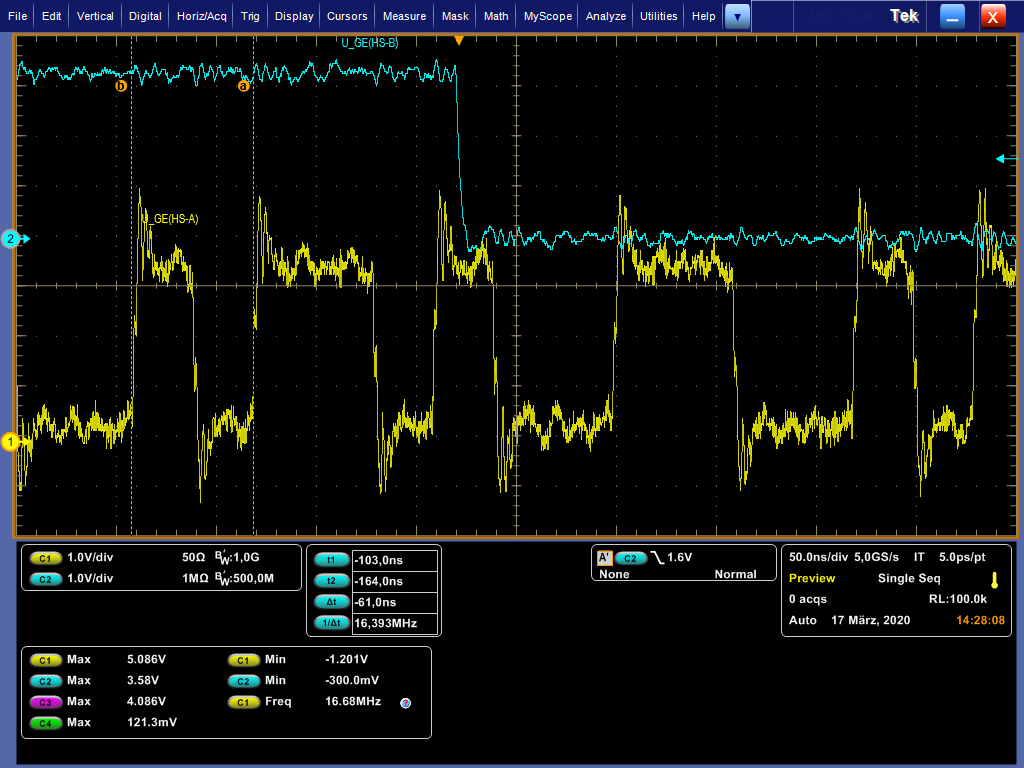

在图片上、您可以看到每次 TMS 有新数据可用时、通道1上的 Σ-Δ 数据流和切换输出。

我假设每次获取新值(DPX 图片上的蓝色线条)所需的时间较长时、都会得到错误的值。

由于我使用光纤电缆在应用中传输数据流、因此我还了解了高电平和低电平状态的不同时间、因为光纤电缆通常会稍微延迟上升沿。

我意识到、如果边沿的延迟在10ns 范围内、无论数据流的运行频率是多少、都会损坏数据。

那么、您是否有详细说明、SDFM 是如何工作的、以及必须满足哪些限制? 为什么它被限制为8...20*t_SYSCLK 的频率? 您只是对信号进行过采样、过采样后的算法是什么? 因为技术参考手册的真正短的限制是不够的。

我将专门讨论上升时间、保持时间、甚至是对实现的描述都非常有用。 因为像这样、我根本就不能使用 TMS。 使用 FPGA 对我来说更有意义。