主题中讨论的其他器件:LAUNCHXL-F28379D

尊敬的 TI C2000专家:

我们在 TMS320F28377SPTPT 上遇到了问题:

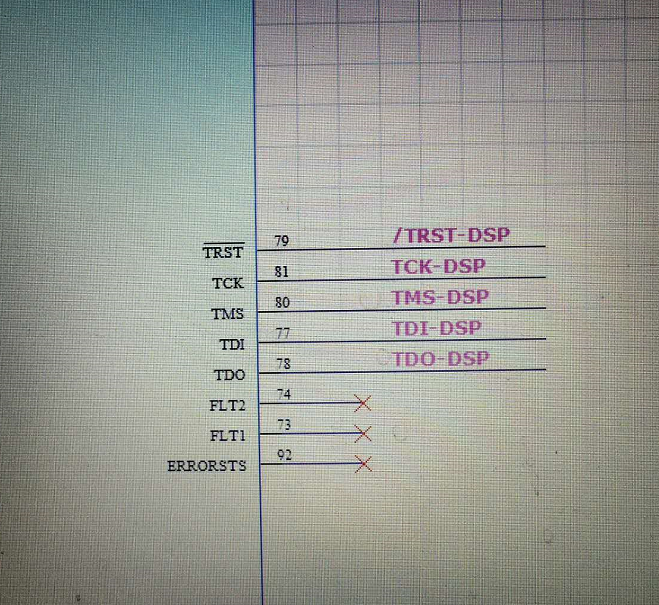

F28377 PCBA---- 14引脚 TJAG---- 仿真器--usb--PC

上面是代码刻录路径;下面是 JTAG sche。

当我们为具有 VDD3.3V 电压的器件加电时、引脚139 (GPIO72)电平状态不确定、如果电平为低电平、则会导致器件进入引导模式。

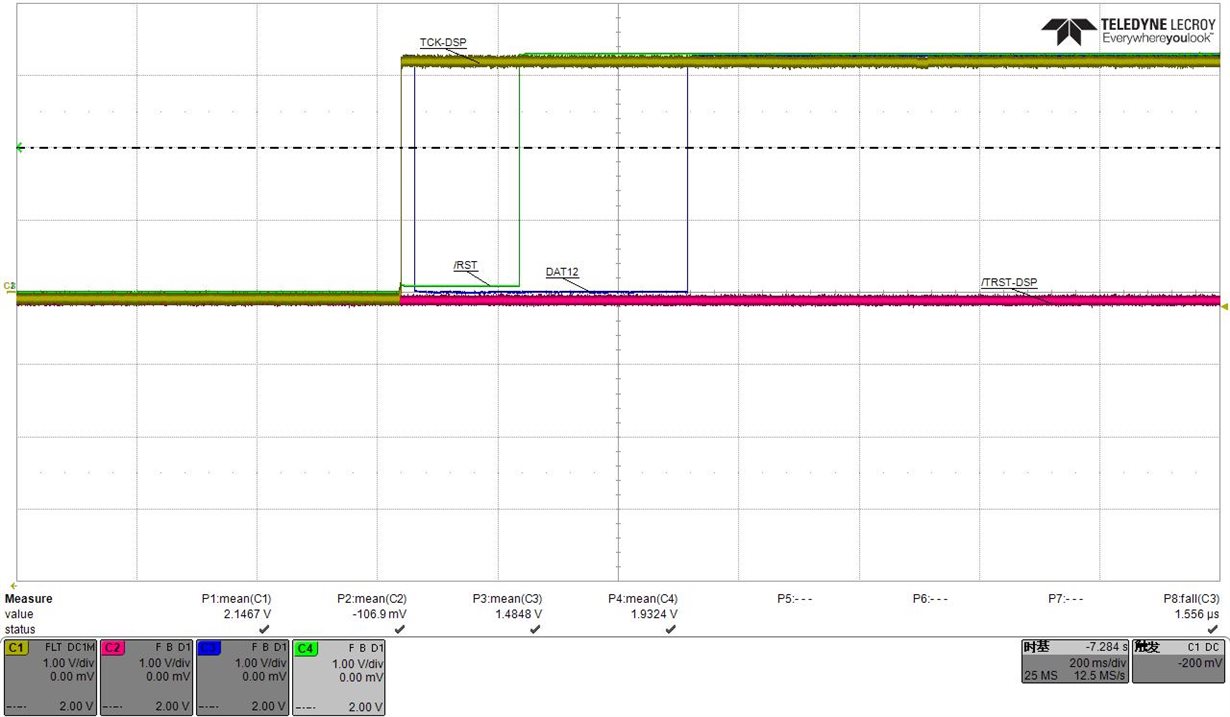

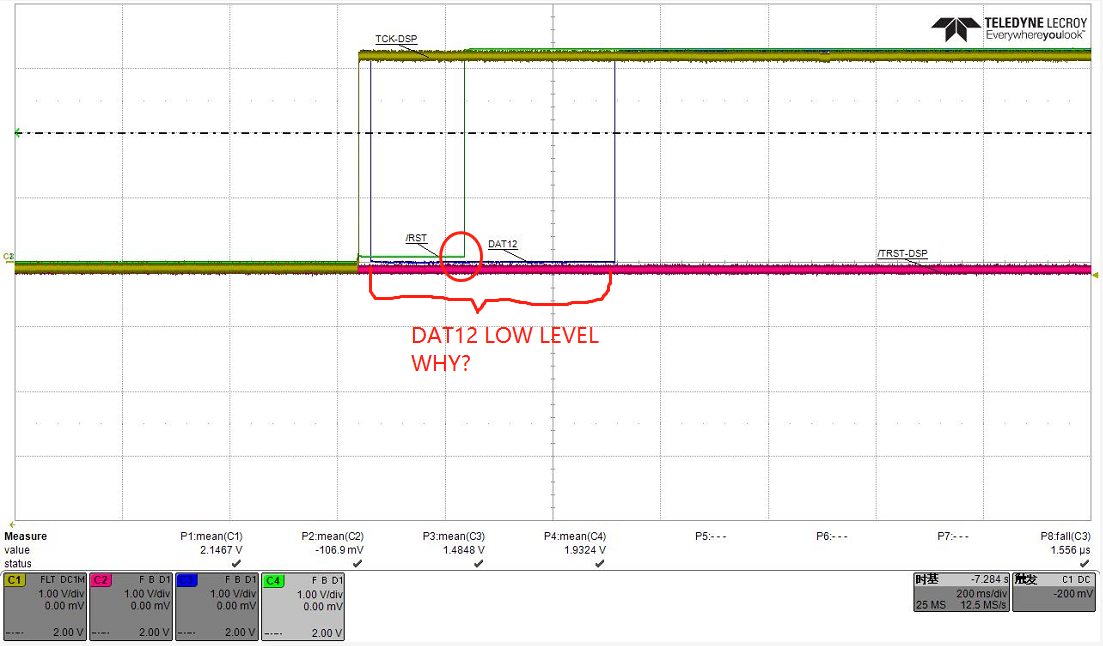

a:当 JTAG 被解插 、然后接通 VDD3.3V 电源时、我们可以检测引脚139/GPIO72/DAT12上的波形、如下图所示、当/RST 被触发时、DAT12为低电平、这会导致器件进入引导模式、这是我们不希望的。

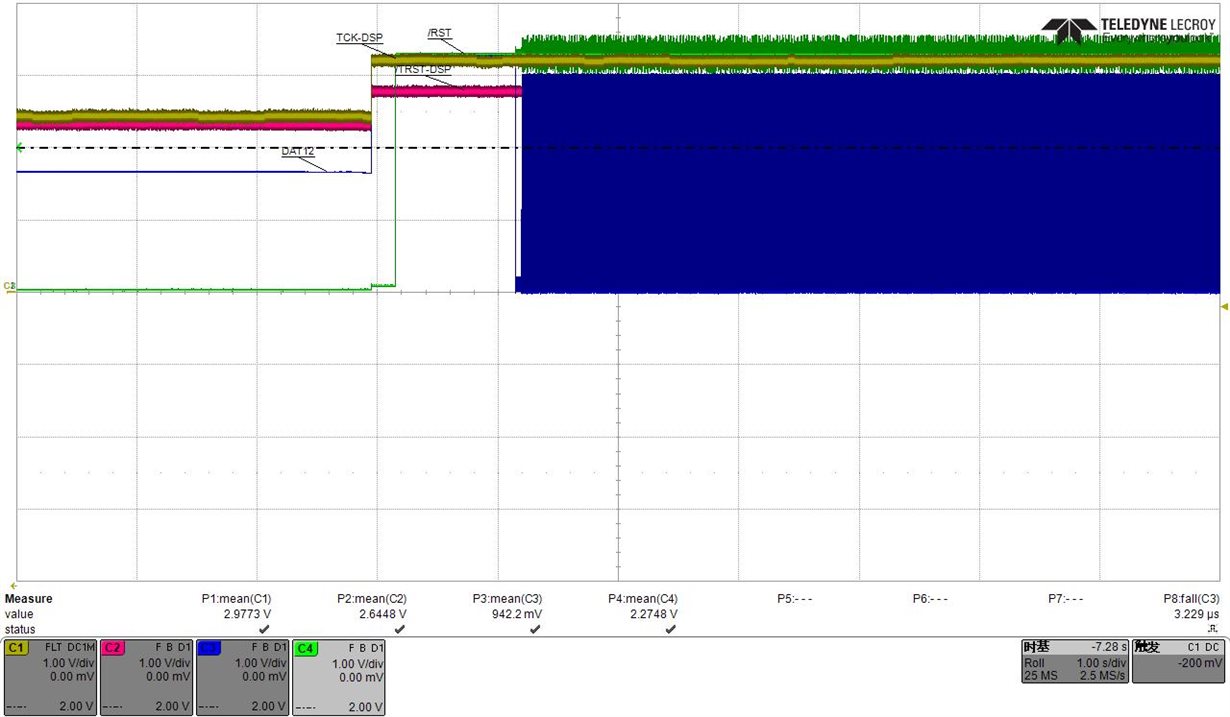

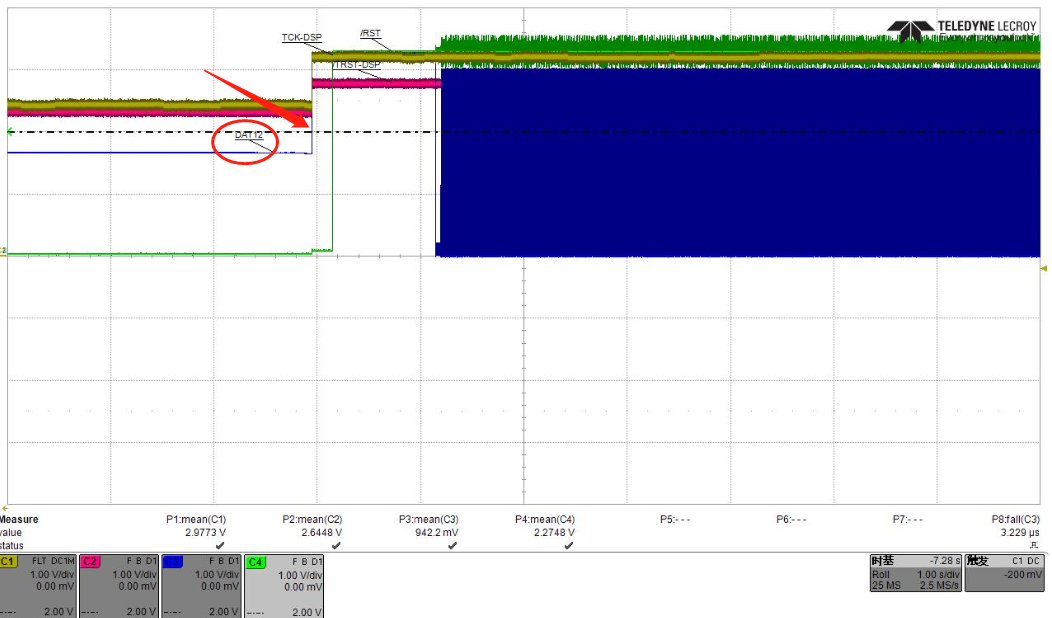

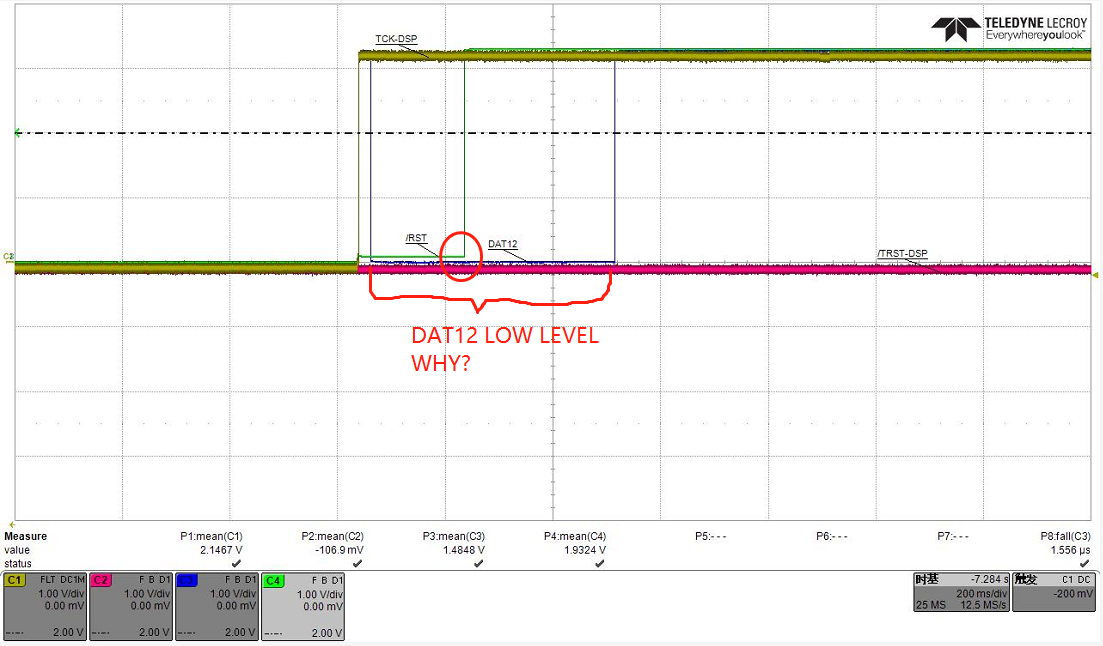

b.插上 JTAG 、然后接通 VDD3.3V 电源时、我们可以检测引脚139/GPIO72/DAT12上的波形、如下图所示、问题是:

1.您是否知道 VDD 网络和 PIN139 (Dat12)上为什么存在不正常的电压(大约1.5V);JTAG 引脚与 GPIO72&VDD 之间的内部电路架构是什么?

2.如何解决此问题(我们不希望器件在器件 RST 之后进入引导模式。)