主题中讨论的其他器件:OPA350、 OPA320、 OPA365

您好!

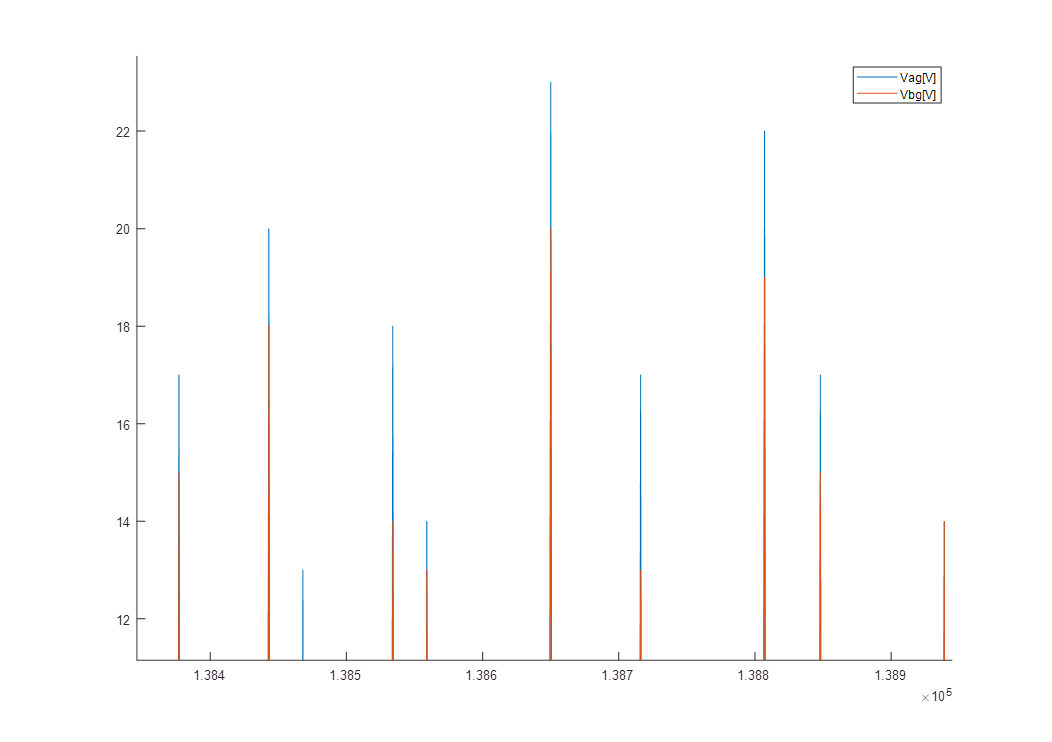

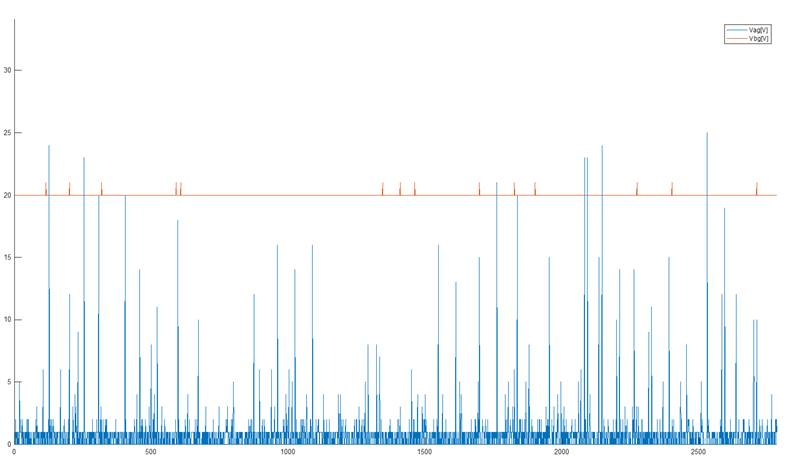

我们正在观察明显的 ADC"火花"。

它甚至出现在短接至模拟 GND (= ADC REF LOW)的 ADC 输入上。

我们观察到的典型噪声在~3-4 LSB 值以内、但通常我们得到的值最多为30 LSB。

我们已经检查了2个不同的板、它们具有相同的行为。

我们不确定这不是 PCB 设计、但我们已经检查了我们可以想到的一切:

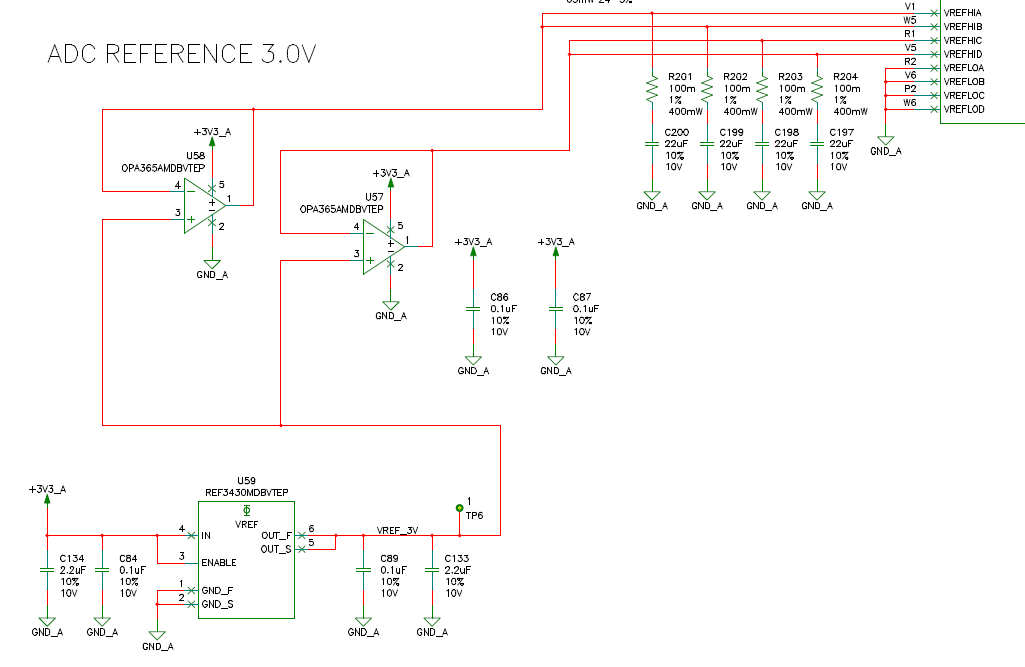

我们已经检查了电源轨、它们是干净的。 我们已经检查了 ADC 基准、就我们在示波器上看到的情况而言、它们是干净的。 我们已确保 AGND 和 DGND 之间的阻抗尽可能好。

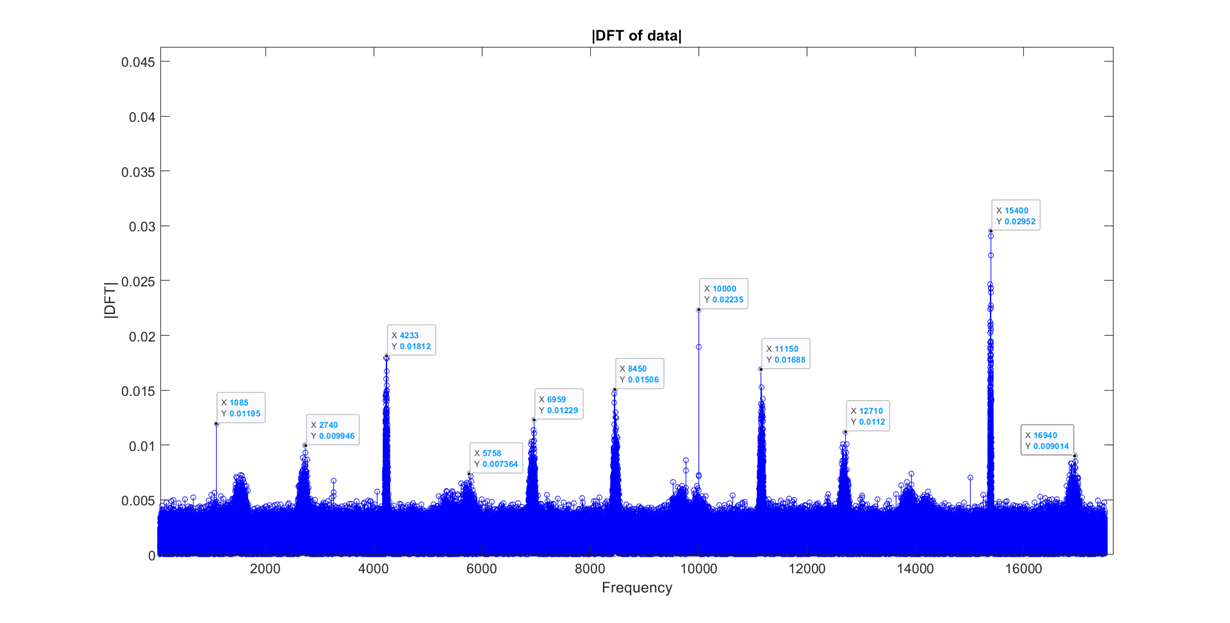

一个有趣的观察是,它似乎是半确定性的... 似乎有几种不同的重复模式(例如每9个样本、每25个样本等)、但它们似乎不是持久的... 可能会出现一些 HF 信号的混叠?

我们以35kHz 的频率进行采样、ADC 稳定时间设置为250ns (我们同时对所有4个 ADC 进行采样、并对6个此类测量进行排序)。 所有测量值的行为都是相同的。

同时在所有同时测量的通道上出现火花(即所有4个 ADC 同时经历、但振幅不同)。

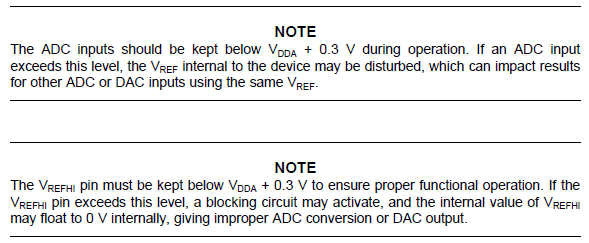

此时、我唯一能想到的是、一些测量的信号实际上等于负模拟轨(=连接到 GND)、并且 AD 转换器将其固定为0、但这不会导致问题、是否可以?

有什么想法吗?

谢谢!

此致、

Ondrej