主题中讨论的其他器件:C2000WARE

大家好,

在附加 的字中,您还可以看到代码和示波器 screndshot,基本上 ,ADC 时序与预期不符:

ADC 时序问题详细信息:

条件

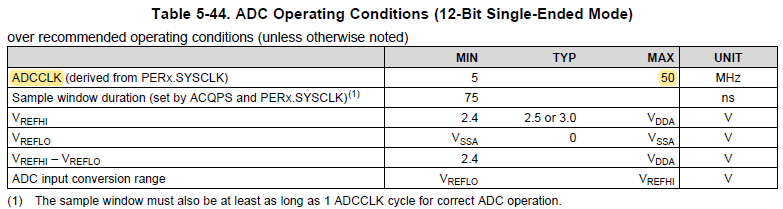

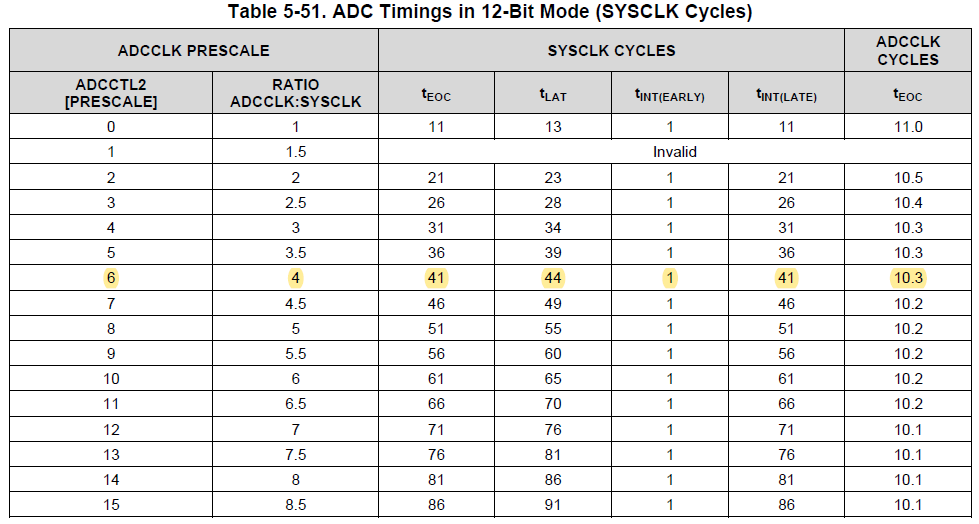

- SYSCLK 为200MHz、为5ns。

- ePWM 在40kHz 周期内触发 ADC SOC。

附加字中的代码

- 使用同一通道 ADCA CH_IN0配置了三个 ADC SOC。

- 仅首先启用 SOC0。 然后、我启用了其余的两个进行比较。 当我这么做时、我还将 ADC_setInterruptSource 更新为 ADC_SOC_NUMBER0或 ADC_SOC_NUMBER2。

附加字中的代码

- 在 SOC2结束时触发 ADC ISR

- 使用 ADC DMA

测试

- 在 ADC SOC0结束时触发 ADC ISR

- 黄色:PWM 同步脉冲

- 蓝色: ADC ISR 启动

- SOC0的 ADC 采样时间为1us (S/H 窗口设置为200、即200 x 5ns = 1us)

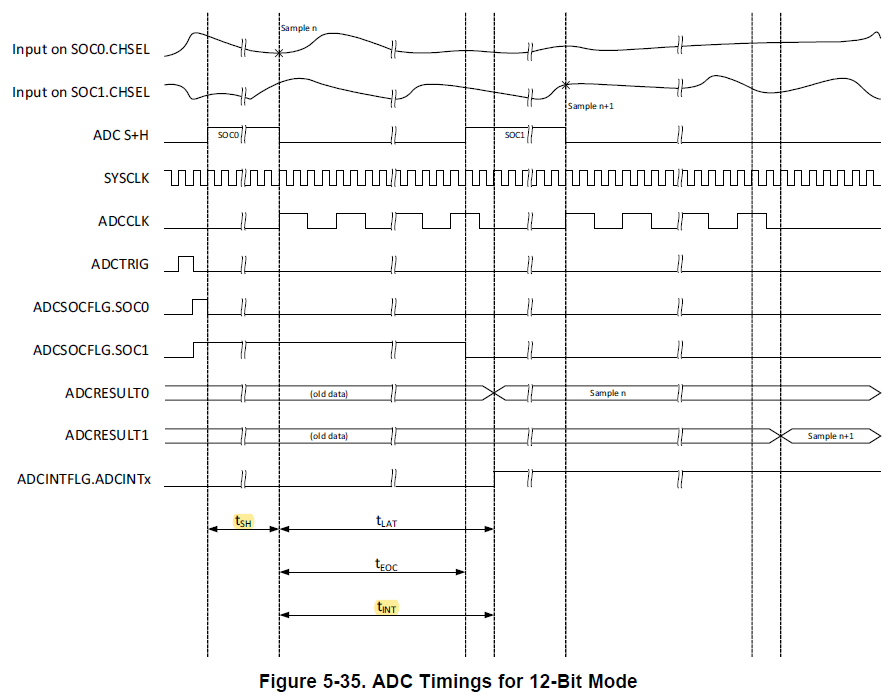

- PWM 同步脉冲上升沿到 ADC ISR 起始点之间的时间大约为1.42us。 我没有包括 GPIO 设置时间延迟、但它看起来额外的420ns 比数据表中规定的值长。

附加字中的作用域

- 在 ADC SOC2结束时触发 ADC ISR

- 黄色:PWM 同步脉冲

- 蓝色: ADC ISR 启动

- SOC0的 ADC 采样时间为2.5us (请参阅上面的代码。 S/H 窗口设置为500、即500 x 5ns = 2.5us)

- PWM 同步脉冲上升沿到 ADC ISR 起始点之间的时间大约为6.34us。 这不能给我始终如一的结果。 我希望2.5us +延迟。

谢谢你

此致

Carloe2e.ti.com/.../ADC-TIMING-Issues--details.docx