主题中讨论的其他器件:C2000WARE

尊敬的先生:

我们正在开发基于28376s 的控制器,并且在 SPI 从设备传输方面存在一些问题

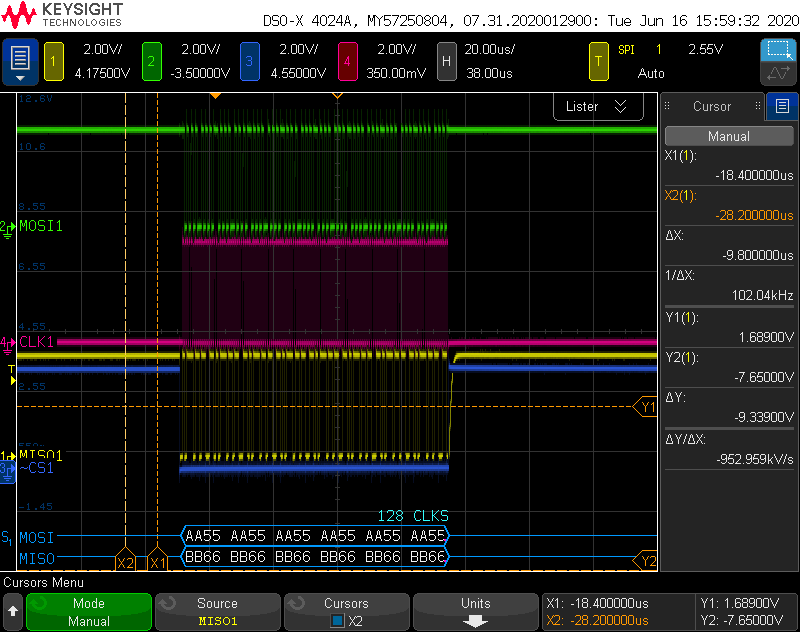

SPI 接口如下所示

1.一个装置配置为 SPI 主设备,发送8个 SPI 字(每个16位)的每个卡盘 (使用 SPI TX FIFO) -不中断

从机数据也从 RX FIFO 中读取(当 FIFO 不为空时),出于测试目的,设备发送 8个0xaa55字 (这在从机端进行验证)

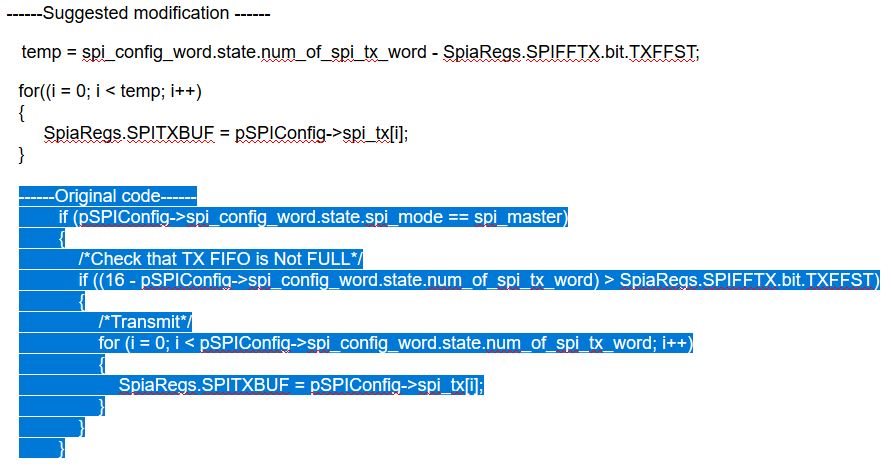

2.秒单元 配置为 SPI 从属设备,每1ms 检查一次 SPI RX FIFO,如果没有空,则读取 FIFO 中所有可用的数据 ,并插入要为下一个 SPI 通信传输的数据

使用主器件,也可以使用8个 SPI 字(16位),出于测试目的,该单元发送8个0xbb66字(这在主器件上已验证)

这是使用各种 SPI CLK ( 2.5MHz、1MHz、400kHz)进行测试 的,问题仍然存在 ,这是从机数据看起来损坏 (就好像它被移动了几位一样) 的时刻,它每5到10分钟发生一次

在 从器件侧写入 SPI TX 缓冲器时是否出现问题(因为它未满)? 我猜、当从器件在与 SPI 主器件通信的同时写入 SPI TX FIFO 时、可能会有一些冲突

但我认为在写入 FIFO 而不是直接写入 SPIDAT 时应该会出现任何问题

请就此 事项提出建议