尊敬的先生:

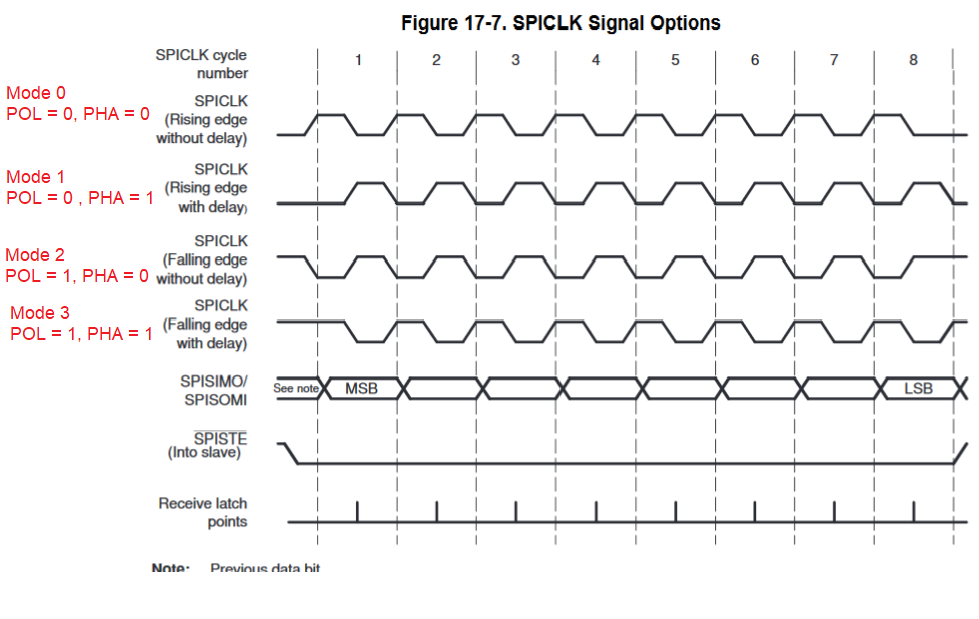

我们正在开发基于28376S 的控制器 、但 在达到指定的 SPI 配置方面存在一些问题。我们的控制器是 SPI 主器件、每个 12位发送3xSPI 字 、SPI 时钟为1MHz、

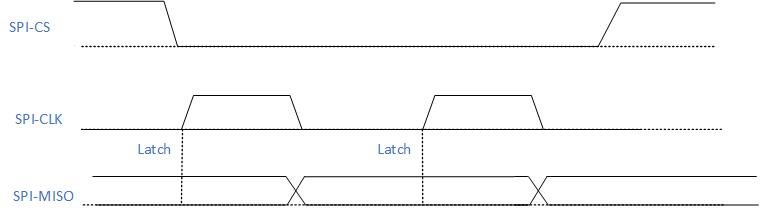

从机时钟方案 在下降沿(这也是我们配置的方法)上计时数据,并在上升沿(SPI 主设备也是如此)上锁存。

我们看到的问题是在设置时钟极性=1 ( 例如,下降时的移位和上升时的锁存)时 ,SPI CLK 在帧开始期间处于高电平(例如 CS 将变为低电平),这会导致我们漏掉1位

我们需要的是在帧开始期间以低电平启动的 SPI 时钟 ,但在上升沿锁存 ,如下所示,如何实现它?