主题中讨论的其他器件:LMH6715

你(们)好

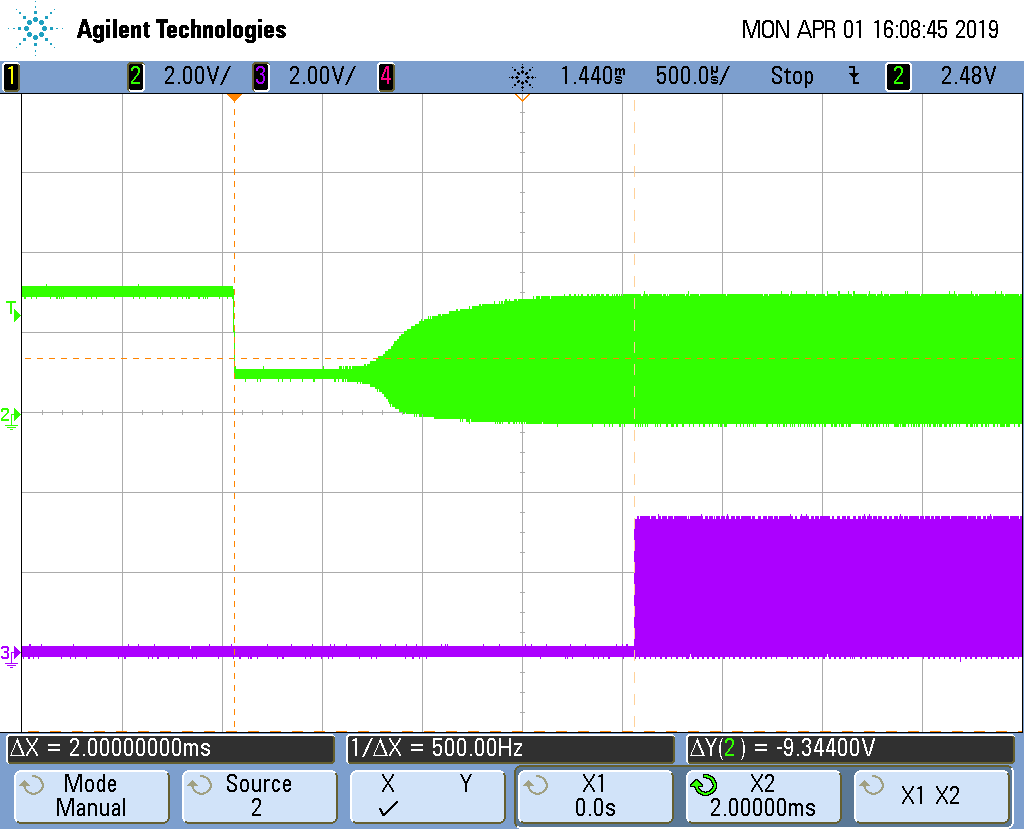

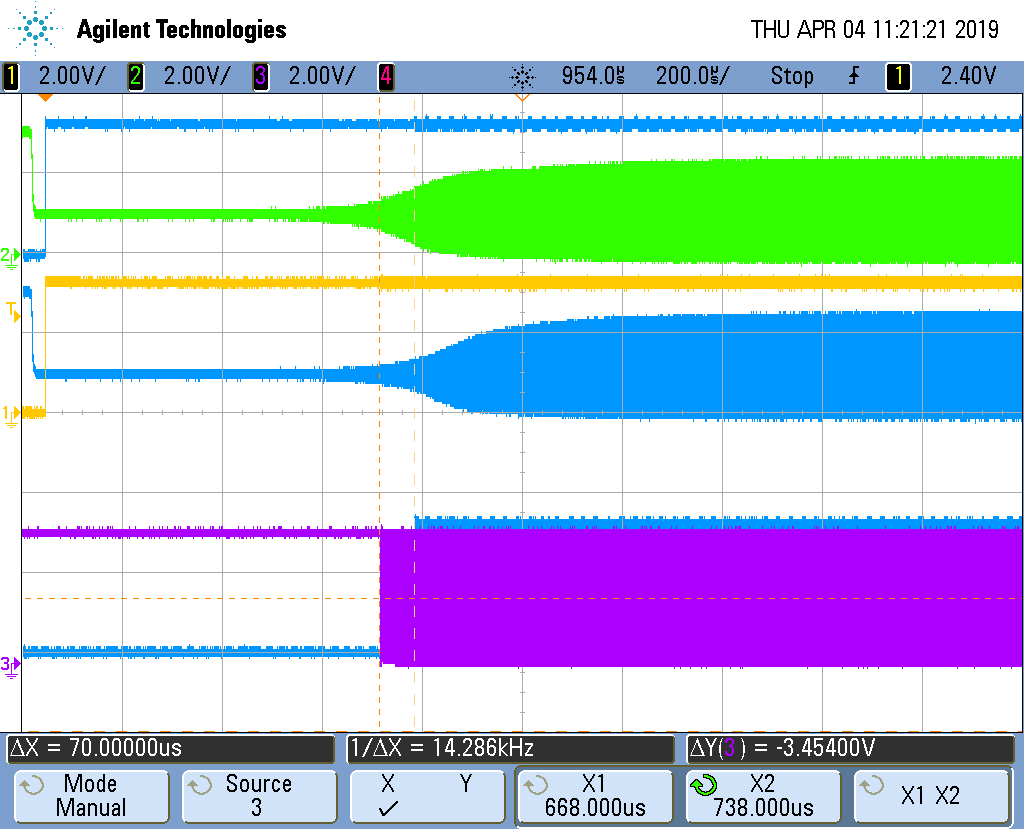

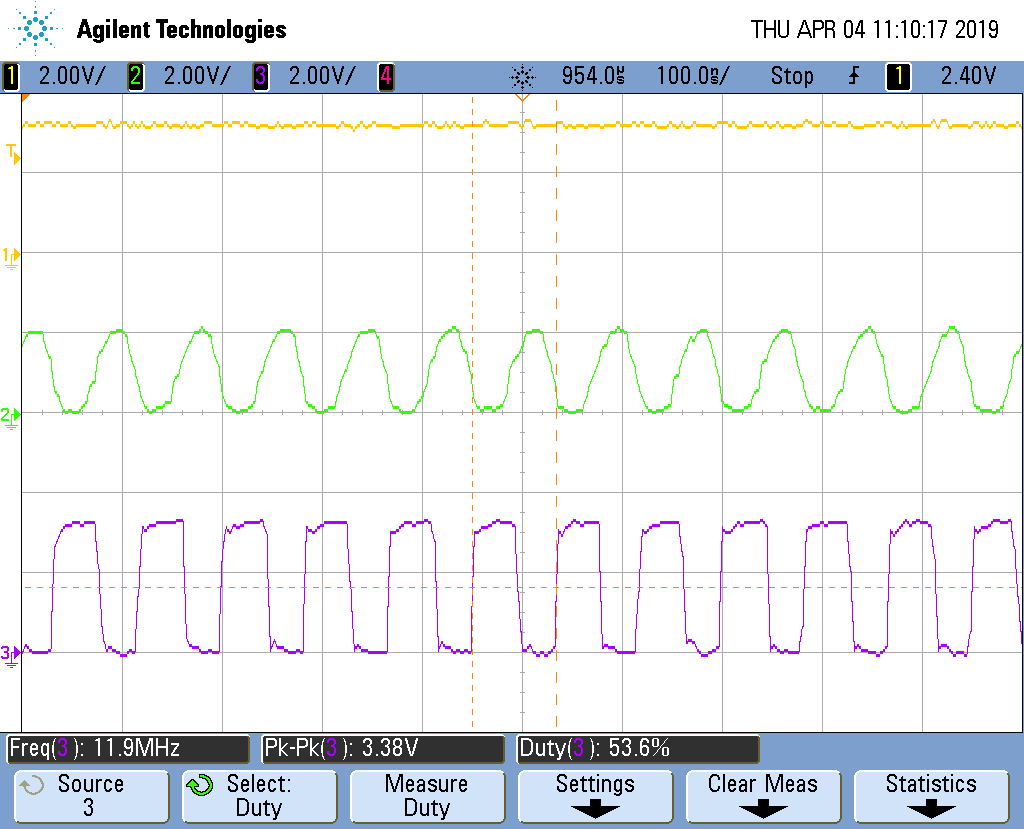

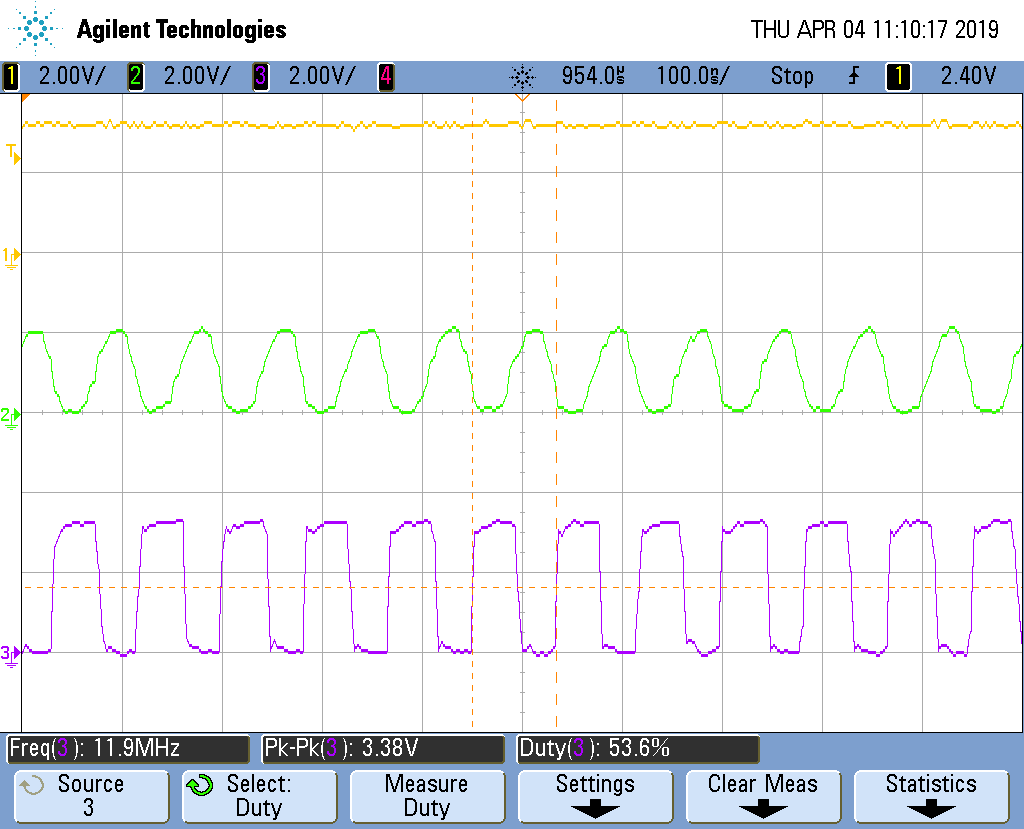

我一直在测量 我们使用的28069微控制器板上的晶体信号。 主要是确保晶体不会过驱(或欠驱动)、并且具有足够的增益裕度、以便在给定的容差和 极端温度下可靠启动。 随着我们 转向280049、我想测量280049 LaunchPad 晶体振荡器。 由于我没有昂贵的电流探头或 FET 电压 探头、我构建了一个具有2pF 输入电容的单位增益宽带缓冲放大器。 我测量的是3.16Vpp (峰峰值)、当然还有一个直流失调电压。 这 似乎与280049的技术规格一致、该技术规格的振荡器电压大于 28069规定的1.8V。

ESC-200-18-30B 晶体的额定工作频率为20MHz 18pF 40 Ω 100uW 最大值

如果您使用振荡器设计指南中 ST 引用的公式、用户可以 根据电压估算晶体驱动功率。

PD = IRMS^2 * ESR

IRMS = 2 π F * CT * Vpp/(2 * sqrt (2))

CT = C1 +(杂散/2)+ Cprobe = 15pF +? + 2pF。 假设 CSTRAY = 4pF (引脚输入电容+ PCB 电容) 、则 CT = 19pF。

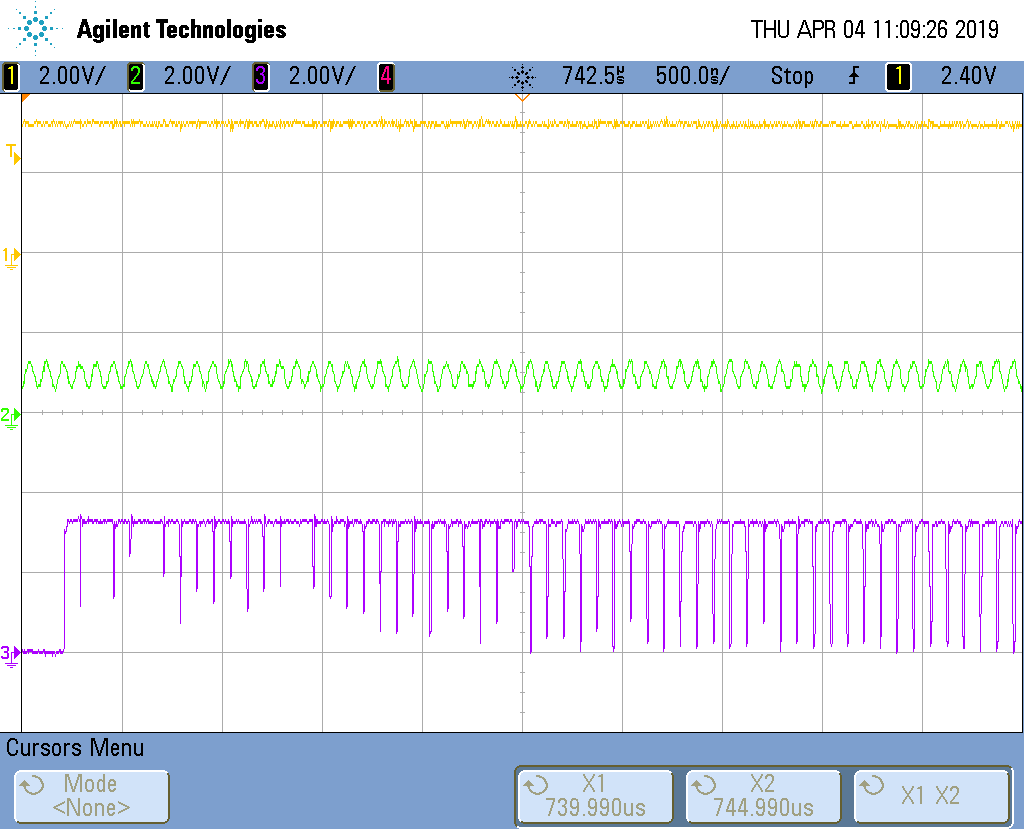

这样便得出 PD = 2.66mA ^2 * 40 = 284uW、晶体的额定最大功率为100uW

好的、它是一个开发板、40欧姆是 ESR 最大值 没什么大不了的?! 我还拥有一些预制电路板、这些电路板的 最大功率为200uW、最大功率为100uW 晶体、短期内没有问题。 但是 、与其他制造商相同的晶振尺寸规定 PD 最大值为300uW。 我不是晶体专家、也不知道 max 之间的统计差异是多少 ESR、并且典型的可能性为。 我也不能保证上面 的公式、但我已经使用了它、并将结果与 频率为12MHz 的晶振的电流测量结果进行了比较(请参阅后面我使用的探针)、结果是相当的。

真正的重点是 TI 提供 的有关晶体振荡器设计的一般信息很少。 数据表中的语句为:

"TI 建议晶体制造商使用应用板对晶体进行特性分析"-实际上没有太多帮助。

例如、没有有关振荡器跨导的信息、这是 一个在开始测量之前计算可能的增益裕度的有用数字。 如果您采用开发板设计、那么您可能会在稍后 的现场遇到问题-或者可能不会。

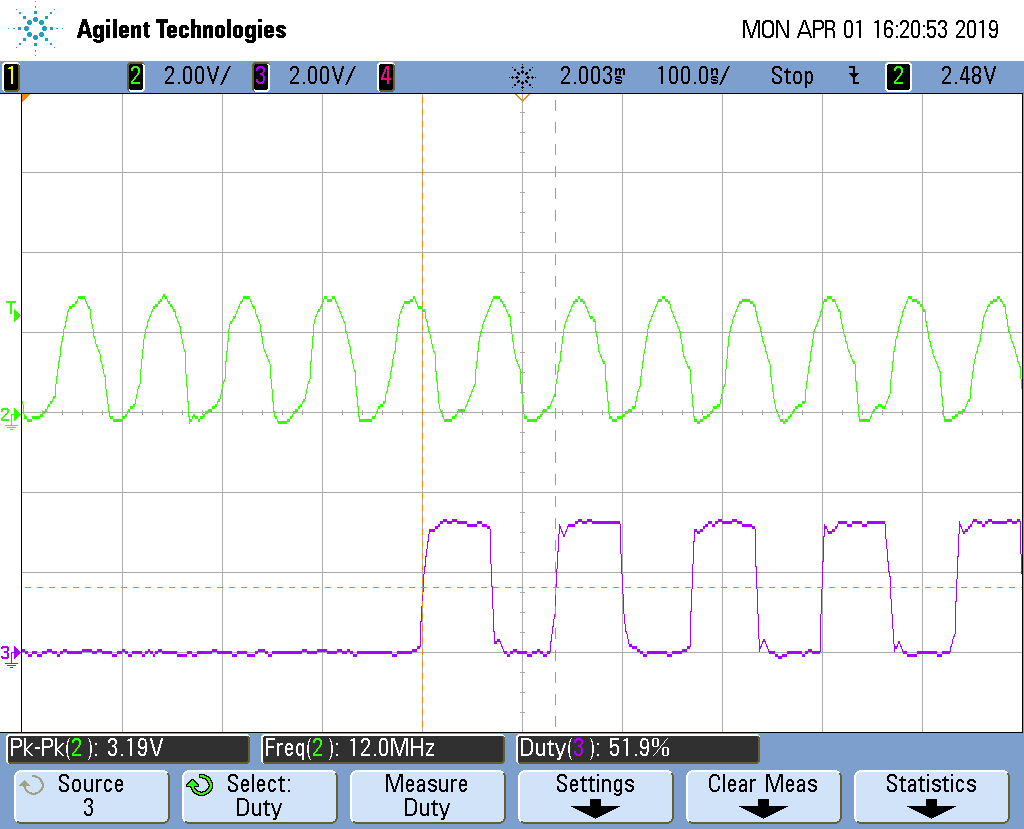

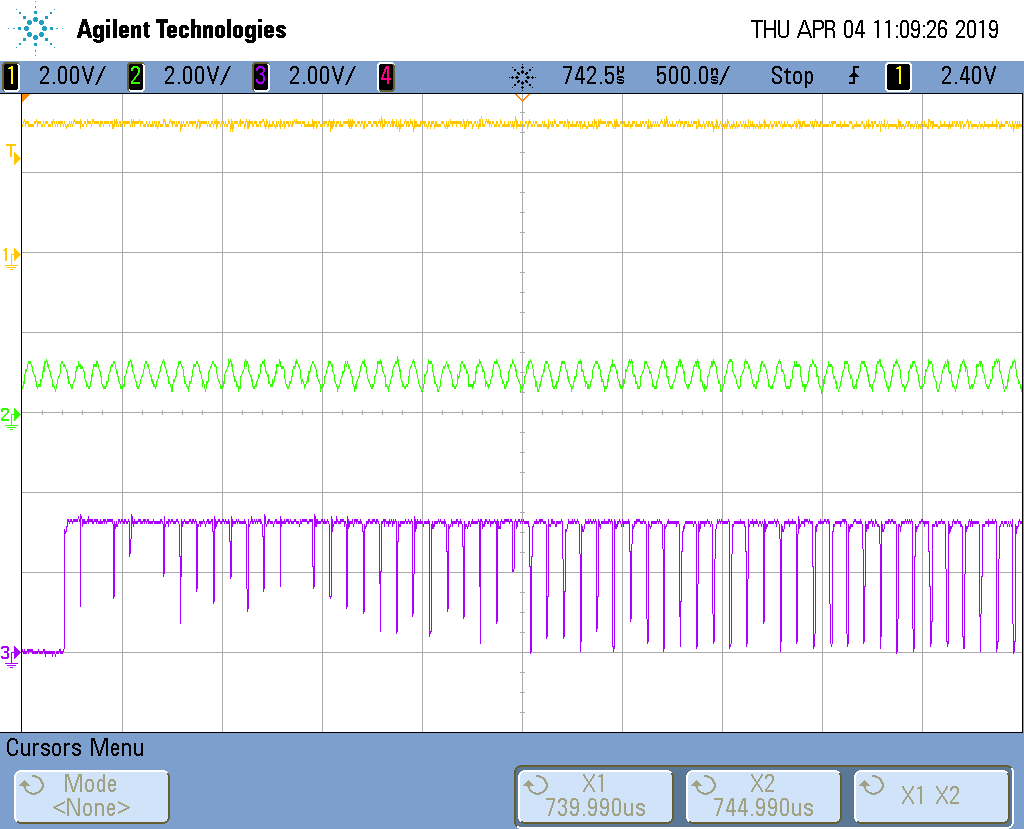

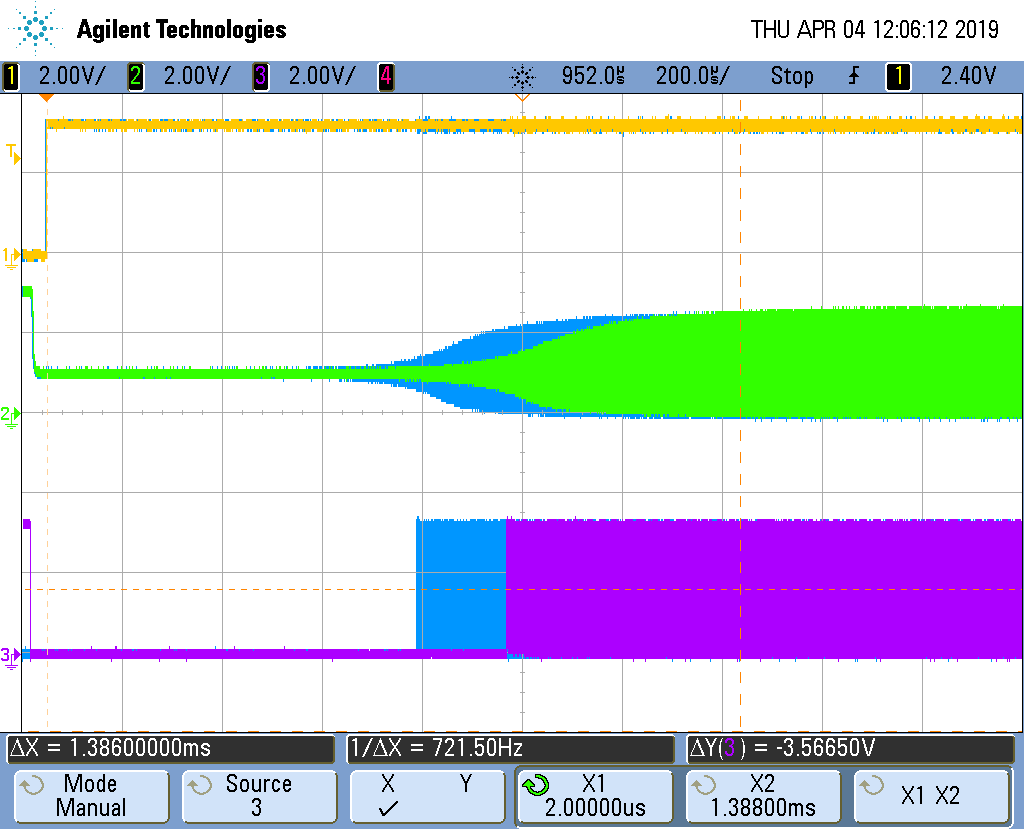

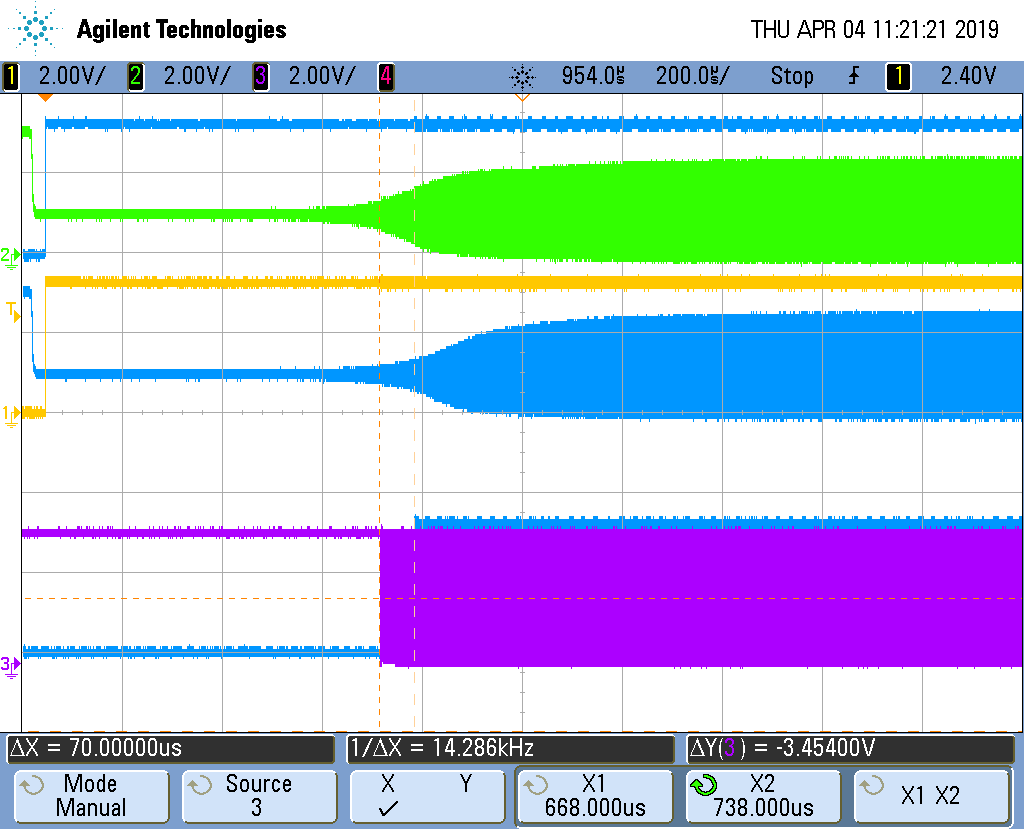

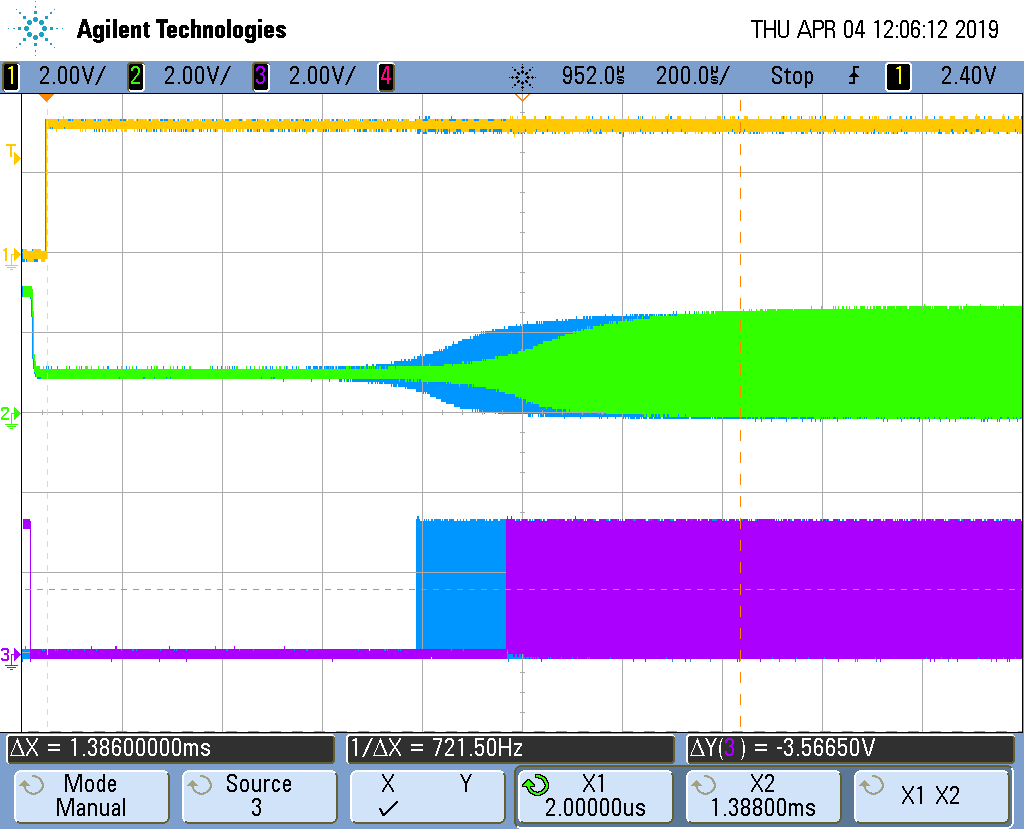

如果您想在不使用昂贵电流探头的情况下测量晶体中的电流、我还完成了以下操作来测量10-12MHz 晶体:

39个导通端接390欧姆(10mV/mA)的4C65 TN10/6/4镍锌铁氧体磁芯。 将一些薄型同轴电缆作为主芯片通过、并与晶体串联-所有引线尽可能短。 将屏蔽层的一端接地至振荡器/微接地。 然后、您需要2级或更多级 宽带宽 运算放大器、每个放大器的增益为3 - 4。 我使用了两个 AD8039放大器、每个放大器具有4个增益、但电流反馈类型 LMH6715可能更好。 应用高频布局 请参阅 Jim Williams'

www.analogue.com/.../dn101f.pdf

输出50欧姆的放大器、并在 示波器上以50欧姆结束。 我通过 测量 Keysight 函数发生 器的电流输出对探针进行了校准、其50 Ω 输出短路。 或者、使用较高的电阻值、即1K 并设置为2Vpp、以获得2Vpp/1050ohm = 1.9mApp。 引线尽可能短!

最后、我知道我犯了错误(相信我!) 因此、不要接受我在阅读时所说的内容-尝试自己测量晶体振荡器并得出自己的结论。 我希望 TI 在未来会对该主题提供更多支持。

谢谢