F28027控制卡的 EPWM1输出设置为切换输出时出现问题、如下所示:

EPwm1Regs.AQCTLA.bit.ZRO = 0x3;//当计数器= 0时、切换 EPWM1A 输出

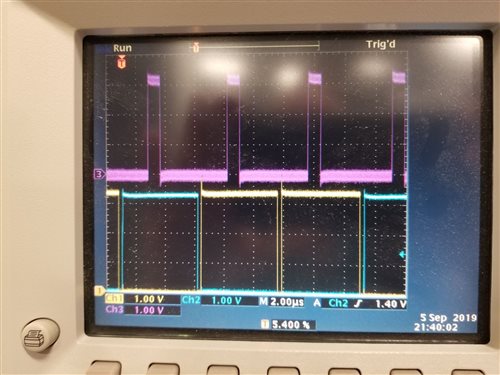

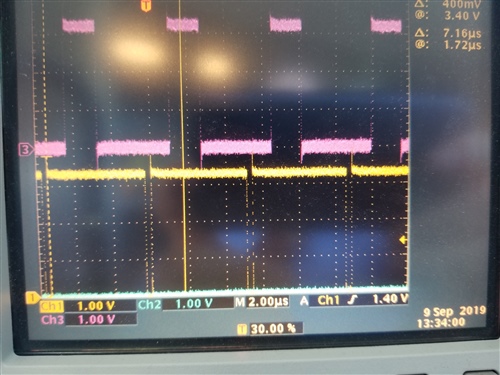

问题如下所示。 黄色走线为 EPWM1A、蓝色走线为 EPWM1B。 在该单次触发跟踪中捕获 EPWM1A 的两个连续脉冲。 (粉红色迹线是 EPWM4、用于生成 ISR 和斜坡启动时序)。

我已设置 EPWM1、因此比较器可以生成同步事件、将 TBPHS 值(=0)加载到时基寄存器中。 如果比较器未跳闸、则 EPWM1将复位为 MAX_PERIOD 值。 当比较器在 MAX_PERIOD 之前跳闸时、发生双脉冲、以便比较器同步与 MAX_PERIOD 同步或几乎与 MAX_PERIOD 同步。 此处显示的波形是通过直流电压生成至比较器输入的、并且没有由 ePWM 输出控制的开关电子器件。

是否有任何方法可以抑制这种双脉冲? 如果我将开关电子器件实际连接到控制器、这种行为将是灾难性的。

以下是相关代码:

EALLOW;

//配置 ePWM1AB (用于切换初级半桥 FET)

PWM_ComplPairDB_CNF (1、MAX_PERIOD、1、0);//使用互补输出配置 EPWM1、1=主控模式、0=相位

EPwm1Regs.TBCTL.bit.SYNCOSEL = TB_CTR_ZERO;//当计数器= 0时同步输出

EPwm1Regs.TBCTL.bit.PHSEN = 1;//启用从相位寄存器加载计数器寄存器

EPwm1Regs.TBPHS.Half.TBPHS = 0;//相位寄存器值

EPwm1Regs.TBCTL.bit.PHSEN = 0x1;//导致计数器在 SYNC 变为 TBPHS

EPwm1Regs.TBPHS.Half.TBPHS = 0x0;//在 SYNC 设置计数器为0

EPwm1Regs.DCTRIPSEL.bit.DCAHCOMPSEL = DC_COMP1OUT;// 8 = DCAH =比较器1最初输出(在 Comp1和 Comp2之间交替每个相位)

EPwm1Regs.TZDCSEL.bit.DCAEVT1 = TZ_DCAH_HI;// 2 = DCAH 高电平上设置的 DCAEVT1 (当比较器输出变为高电平时将变为有效)

EPwm1Regs.DCACTL.bit.EVT1SRCSEL = 1;// 1 =源为 DCEVTFILT 信号(由事件窗口过滤、见下文)

// EPwm1Regs.DCACTL.bit.EVT1FRCSYNCSEL = 0;// 0 = DCAEVT1.FORCE 的同步路径

EPwm1Regs.DCACTL.bit.EVT1SYNCE = 0x1;// 1 =同步生成启用

EPwm1Regs.TZCTL.bit.DCAEVT1 = 0x3;//事件发生时不对 EPWM1A 输出执行任何操作

EPwm1Regs.DCFCTL.bit.SRCSEL = DC_SRC_DCAEVT1;// 0 =滤波器源= DCAEVT1

EPwm1Regs.DCFCTL.bit.PULSESEL = DC_PULSESEL_ZERO;// 1 = TBCTR 上的滤波器启动= 0

EPwm1Regs.DCFCTL.bit.Blanke = DC_BLANK_ENABLE;// 1=启用消隐窗口

EPwm1Regs.DCFCTL.bit.BLANKINV = 0;// 0 =消隐窗口未反转

EPwm1Regs.DCFOFFSET = 0;//滤波器偏移

EPwm1Regs.DCFWINDOW = min_period;//缓存在斜坡被触发后结束

EPwm1Regs.AQCTLA.bit.ZRO = 0x3;//当计数器= 0时、切换 EPWM1A 输出

EPwm1Regs.AQCTLA.bit.CAU = 0x0;//不执行任何操作(禁用操作)

EPwm1Regs.AQCTLA.bit.PRD = 0x0;//不执行任何操作(禁用操作)

PWM_ComplPairDB_updatedb (1、红色、FED);//设置死区时序

//配置 PWM2A

PWM_1ch_UpCntDB_Compl_CNF (2、MAX_PERIOD、0、0);//将周期更改为 MAX_PERIOD

PWM_1ch_UpCntDB_Compl_updateedb (2、REM1、FEM1);

//配置 PWM3A

PWM_1ch_UpCntDB_CNF (3、MAX_PERIOD、0、0);//将周期更改为 MAX_PERIOD

PWM_1ch_UpCntDB_updatedb (3、REM2、FEM2);

//配置 EPWM4

PWM_1ch_CNF (4、MAX_PERIOD、0、MIN_PERIOD+MIN_Delta);//更改为从器件、周期更改为 MAX_PERIOD

// EPwm4Regs.CMPCTL.bit.SHDWAMODE = 1;//立即模式。 仅使用活动比较 A 寄存器。

EPwm4Regs.CMPA.half.CMPA = MAX_PERIOD-50;//设置 EPWM4输出脉冲启动和 CNTL_ISR 的触发点

EPwm4Regs.AQCTLA.bit.ZRO = 0x1;//输出低电平

EPwm4Regs.AQCTLA.bit.CAU = 0x2;//输出高电平

EPwm4Regs.AQCTLA.bit.PRD = 0x0;//不执行任何操作(禁用操作)

//配置比较器和斜坡发生器块

DacDrvCnf (1、0x7FFF、1、4、斜率); //为 PQMC 添加了:COMP1、DACVAL=max Q15、DACSOURCE=rampgen=1、RAMPSOURCE=PWM4

Comp1Regs.COMPCTL.bit.SYNCSEL = 0;//不过滤比较器输出

DacDrvCnf (2、0x7FFF、1、4、斜率); //为 PQMC 添加了:COMP2、DACVAL=max Q15、DACSOURCE=rampgen=1、RAMPSOURCE=PWM4

Comp2Regs.COMPCTL.bit.SYNCSEL = 0;//不过滤比较器输出

EDIS;

感谢您的帮助、

Ciaran