主题中讨论的其他器件:TLV6001、 ISO224、 ISO224EVM

工具/软件:WEBENCH设计工具

您好!

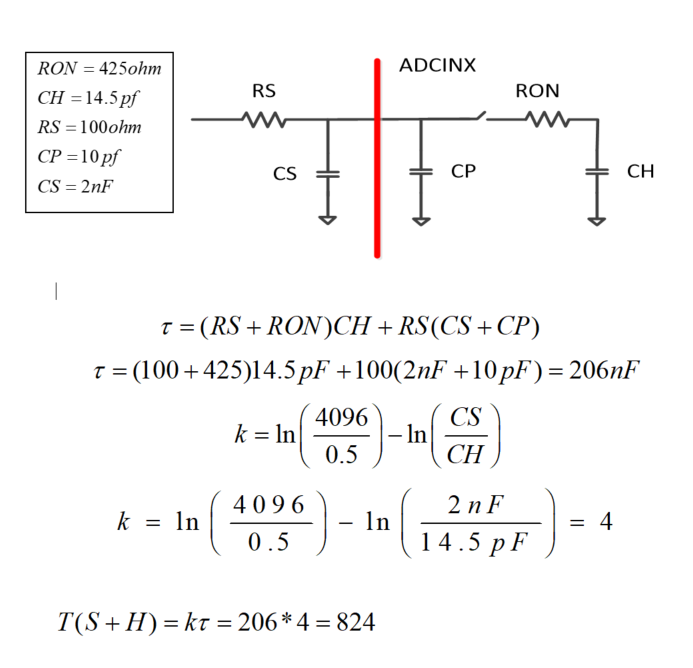

对于我的实验、我使用的开关频率为50kHz、ADC 采样频率应比开关频率大4或5倍。 我想为200kHz 采样频率设计 RC 桶电路和 ACQPS。 我选择了 CS 2nF。 适用于200kHz 采样频率吗? 是否需要增加或减少 CS? 我不确定是否可以随着采样频率的升高而增大或减小 CS。 TI 建议 CS 至少应比 CH 大10或20倍。 如何选择 RS? 我计算 ACQPS 是否正确 ? 我仍然不理解 ADC 采样和充电电路桶电路之间的关系