您好、C2000冠军

我的客户将 GPIO54~GPIO57用于 SINC 函数、将 GPIO58~ GPIO61用于 SPI 以访问 EEPROM。

来自 FPGA 的 SPI CLK 2.5MHz、正弦 CLK 8MHz。

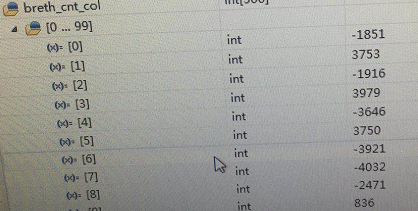

当 SPI 将数据写入 EEPROM 时、SINC 数据寄存器具有 杂散数据。 测试完成后、我们发现 SPI_MOSI/GPIO58会影响 SINC、甚至切断 GPIO58引脚的导线、问题仍然存在。

有两种方法可以解决、一种是不使用 GPIO58作为 SPI_MOSI、但使用 GPIO16、另一种是将 SPI 时钟降低到1MHz 以下。

请帮助检查此问题。

谢谢!