主题中讨论的其他器件:TMDSCNCD280049C、 TMDSHSECDOCK

您好 e2e、

一个月前 、我收到了 带有集线板 TMDSHSECDOCK 的控制卡 TMDSCNCD280049C、一直在尝试使用它们。 使用 CCS 平台的最初步骤始终失败、因为我从未成功测试与控制卡的连接。 我总是收到 以下错误-" JTAG DR 完整性扫描测试失败 "。 我尝试了以下测试设置:

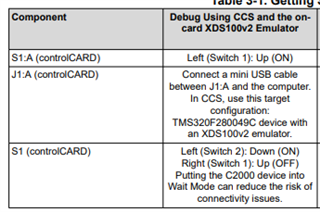

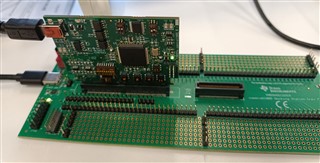

1.将控制卡插入扩展坞后、两块板都通过 USB 连接到 PC、即扩展坞中的 J17通过 USB 连接到 PC (S1也通过 USB-ON 连接)、J1:A 输入控制卡也通过 USB 连接。 如下图所示、LED D1 (在 TMDSHSECDOCK 上)和 D2:A 和 D1 (在 TMDSCNCD280049C 上)都将亮起。 但是,我仍然得到 " JTAG DR 完整性扫描测试失败 "每次我都尝试测试连接。

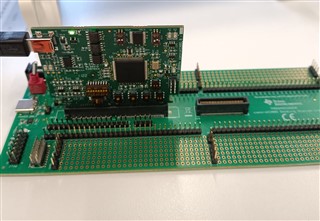

2. 将 controlCard 插入对接板时, TMDSHSECDOCK 中只有 J17是 USB 连接到 PC (S1也是 USB-ON),我收到另一个错误。 软打开控制器时出错。 "请查看下面的设置、

3.在只 提供 USB 连接到控制卡 TMDSCNCD280049C 的情况下,我得到与第一例相同的连接失败错误, " JTAG DR 完整性扫描测试失败 "。 我明白,在所有情况下, 由于控制卡不接收 TMDSHSECDOCK 的电源,所以必须提供 USB 连接到 TMDSCNCD280049C (在 J1:A 上) 。 是这样吗?

下面是此设置的照片。

您能不能帮助弄清楚这些错误是什么以及如何解决这些错误?

谢谢。