请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:TMS320F280025 大家好、

客户有一些问题需要您的帮助:

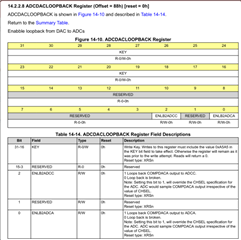

1.我没有看到 TRM 和 DS 中 DAC 到 ADC 环回的任何示意图、因此我想知道它是如何环回的?

2.模拟子系统中有四个比较器,每个比较器都有两个高电平和低电平 DAC。 因此、总共有8个 DAC。 下图 COMPDACA 指的是哪个 DAC? 并连接到哪个 ADCA 和 ADCC 通道?

您能帮助检查这个问题吗?

谢谢。此致、

本