请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:TMS320F280041-Q1 尊敬的 BU 专家:

客户向我提出一些问题、需要您的帮助:

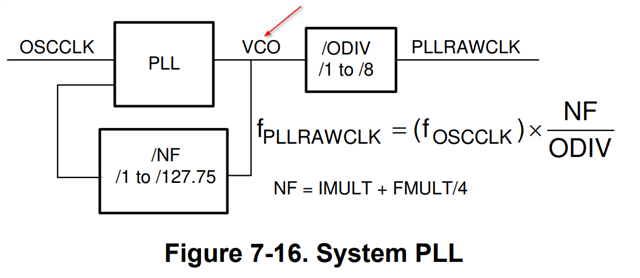

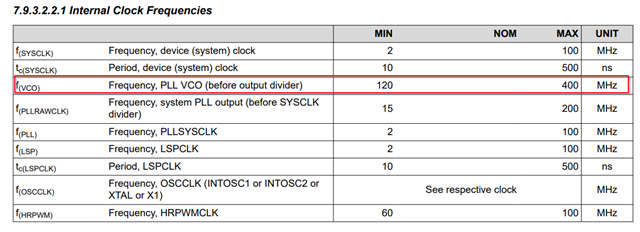

1)。 如果 PLL 电路中的 VCOCLK 不满足数据表中显示的规格要求、将会发生什么情况? 根据客户的配置、f (VCO)将为100m。 他们希望知道此配置的风险。

2)。 如果 f (VCO)< 120MHz、PLL 是否会被器件本身自动旁路、就像时钟丢失检测机制、应用不知道?

此致、

怎样的