主题中讨论的其他器件:TPD1E01B04

大家好

客户正在设计此器件、这是他们的终端设备、并且对设计有一些疑问。 MCU 用于控制板载少数交流继电器。 请注意、在 VDDIO/VDDA (+3.3V)电源轨上观察到+/-50V<5ns 的瞬态尖峰

问题

1.是否会使 MCU 过载并触发和任何保护?

2.在 VDDIO/VDDA 电源轨上部署 ESD/TVS 是否有助于抑制瞬态尖峰? 例如添加 TPD1E01B04

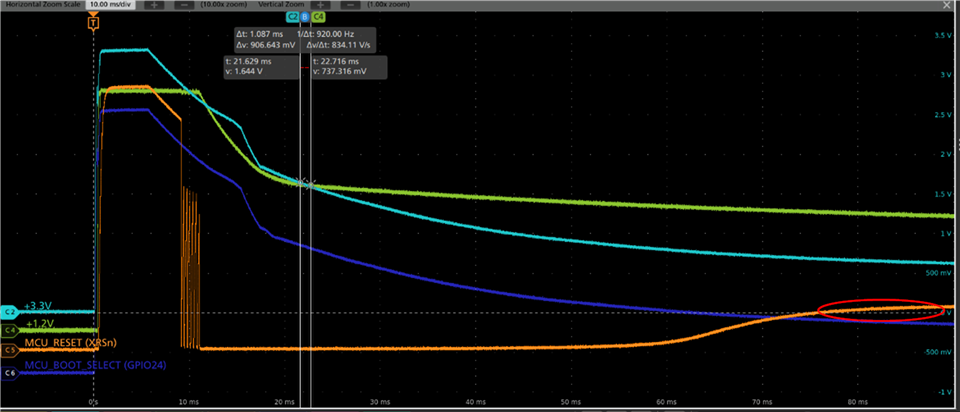

3. VDD 是否有最大电容? 询问的原因是、当设计每个 VDD 引脚使用10uF 和去耦0.1uF (总~40uF)时。 由于没有外部器件连接至1.2V 进行放电、因此结果1.2V 的斜降速度较慢。 这也会导致在断电序列期间、大于10ms 的 VDD (+1.2V)和 VDDIO (+3.3V)之间的电压电平差大于0.3V。 这会引起任何担忧吗?

与 XRSn 引脚类似,在断电过程中,VRSN 引脚和 VDDIO 引脚之间的电压差大于0.3V,这一电压差是否可能损害 MCU?

Rgds

结果