大家好

我想要求提供有关 f28379d 上的 SCI 如何处理错误情况的更多详细信息。

此帖子中有很多问题、因此请仔细阅读、您可以随意地将您的答案分成多个答案。

我将这个问题局限于接收器部分(RX)、还局限于使用 FIFO 的情况。

第一章介绍不同的错误状态位

我已经看到过关于这一主题的其他帖子,但我肯定地注意到结论。

三个寄存器具有错误状态位

- SCIRXST

- RXERROR (FE|OE|PE)

- BRKDT (不总是一个错误,但我还是把它包括在这里)

- 费

- OE

- PE

- SCIRXBUF

- SCIFFFE

- SCIFFPE

- SCIFFRX

- RXFFOVF

我明白不同的错误类型是什么、即组帧错误基本上是一个缺少的停止位 a.s.o。

尚不清楚的是 SCIRXST->FE 和 SCIRXBUF->SCIFFFE 之间的行为和关系。

SCIRXST->PE 和 SCIRXBUF->SCIFFPE 也是如此

让我解释一下我如何理解这一点、然后请纠正我的错误。

想象一下 SCI 接收到5个字节的数据、这些数据都存储在 FIFO 中。

我们将这些字节 b0命名为 b4、其中 b0是第一个到达串行线路的字节、因此位于 FIFO 中。

当 SCI 接收到 B2时、它检测到一个奇偶校验错误。

现在、我明白了这一点。

- 在接收到 B2并检测到奇偶校验错误的时刻、SCIRXST->PE 位将置位、如果启用、将触发错误 IRQ。

- SCIRXST->PE 位将保持置位、直到 SW 发出 SW 复位、方法是将0写入 SCICTL1->SWRESET 位、然后将1写入同一位。

- FIFO 中留出了存储这些信息的空间、因此奇偶校验错误会与字节一起存储。

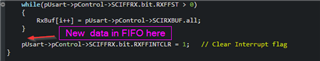

- 当从 FIFO 读取字节时、通过读取 SCIRXBUF 寄存器、我得到 SCIFFPE 位被设置为当并且仅当我读取 B2时

- 由于到 SWRESET 的说明中没有提到这些寄存器、我假设存储在 FIFO 中的错误信息不受软件复位的影响。

因此、读取5次 SCIRXBUF 寄存器后、我就得到了以下结果:

| 字节 |

位15 SCIFFFE |

位14 SCIFFPE |

位13-8 保留 |

位7-0 SAR |

| B0 | 0 | 0 | X |

数据 |

| B1 | 0 | 0 | X | 数据 |

| B2. | 0 | 1. | X | 无效数据 |

| B3 | 0 | 0 | X | 数据 |

| B4. | 0 | 0 | X | 数据 |

- 另据我所知、我必须在一次读取中读取 SCIFFPE 和 SAR、作为只读取 SCIFFPE 的尝试、将计数为读取该寄存器、并从 FIFO 中弹出下一个值。

这一切都意味着我可以得出结论:b0和 b1是有效数据、因为它们在错误之前是接收到的、而 b3和 b4是有效数据、因为它们在错误之后是接收到的、如果它们有效、则在很大程度上取决于其他因素、 但在接收这些寄存器期间未检测到错误。

现在、我们来看看问题的下一章、"发生数据和错误"。

这里、我想的是被移入 RXSHF 寄存器的内容、以及之后在不同错误场景下会在 SCIRXBUF 中启动的内容。

- 在发生奇偶校验错误时、我希望接收到的位存在、只是通过奇偶校验错误位标记为"不良"。

- 当组帧错误发生时、我预期会发生同样的情况、所以在线路上的一个高到低转换触发读取、但是线路又出现了、因此没有停止位、我会在 SAR 中使用零。

- 如果你现在看一下 RXSHF 的内容(我知道它不能从 SW 访问),包括奇偶校验在内的所有零,取决于奇偶校验设置,这可以被检测为奇偶校验错误。 这也会导致奇偶校验错误位的设置、还是被组帧错误排除?

- 从手册进行中断检测时"当 SCI 接收器数据线(SCIRXD)持续保持低电平至少10位、在缺少第一个停止位后开始、便会出现中断状态"

- 这个"缺少第一个停止位"会触发一个组帧错误、还是被中断检测排除?

- "中断的发生 但它不会导致加载接收器缓冲区。"、部分取决于对上一个问题的回答。 "丢失的第一个停止位"之前的数据是否会被移位、从而更改 RXFFST?

最后一章、SW 行为错误。

SW 的行为有时不同于 SCI 的设计人员所期望的:-)

从连接到 CTL 寄存器等的 RX 引脚移位数据的难度有多大。 ?

如果 SWRESET 位或 RXENA 位在接收一个字节的中间被 SW 改变。

- 转换到 RXSHF 是否会暂时停止?

- 如果不是、它会被推送到 SCIRXBUF 吗?

- 如果是、会将已接收到的位推入、这是否会导致检测到奇偶性校验或帧错误?

除了上述错误外、有没有其他方法可以使错误的 SW 触发错误 PE/OE/FE 错误?

如果我要更改奇偶校验位等设置、 首次通信后(无法保证线路静默)、那么建议的步骤是什么?

是的、我的确假定这个过程涉及到清零 RXENA 位、但是

- 我是否需要等待任何事情、例如在更改期间移动正在接收的潜在字节?

- 是否需要清空 FIFO、如果不重新解释 FIFO 中的当前数据、即更改数据大小或奇偶校验设置?

发出软件复位时、首先写入0、然后向 SWRESET 写入1。 我是否需要在写入0和1之间插入暂停?

注意:参考手册"SPRUHM8I–2013年12月–2019年9月修订"第2295页第4行中存在拼写错误

"SCIFFTX 控制接收 FIFO 中断"我认为它应该是"SCIFFRX 控制接收 FIFO 中断"