我们有两种情形、一种按预期工作、DSP 在接收到外部复位后复位、另一种是 DSP 未复位时的故障行为。

我们已经使用了 GPIO5、在 BTLDR 中将其配置为低电平输出、在 app 中我们将 GPIO5配置为高电平。 如果复位完成、BTLDR 将被执行、我们需要看到下降。

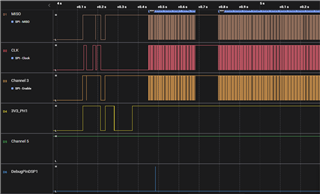

附加了两个具有良好和错误行为的捕获。

*首次测试:

外部复位已完成(灰线)、但是 GPIO5 (白线)未复位。

我们在大约90%的样本中看到这是正确的行为:

*第二次测试:

上电后我们有一个等待复位测试的超时、如果我们检测到超时、我们将 GPIO5设为1。

在下面的捕获中、我们没有看到 GPIO 高电平、因为我们没有达到超时。

这是我们具有的重置电路:

DO_RESET_DSP 是我们的监控器微控制器执行的 DO。 我们在监控 JTAG 连接器中的 PIN XRSn。