主题中讨论的其他器件: C2000WARE、 REF3430、 OPA320、REF5030

尊敬的专家:

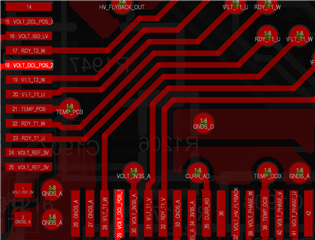

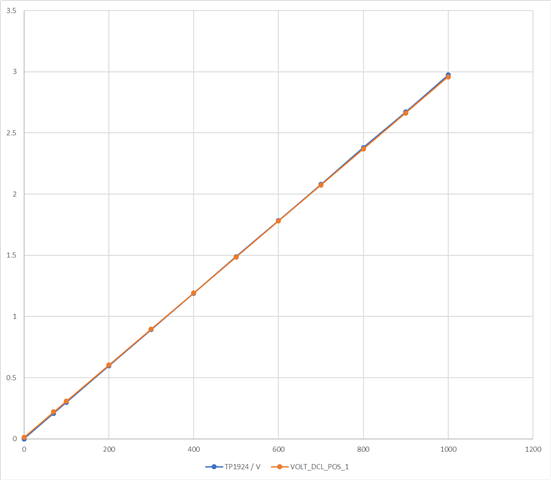

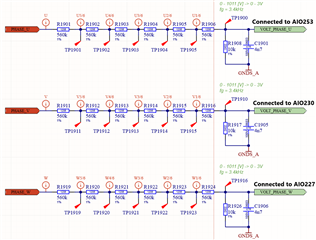

我们当前正在开发适用于 TMS320F280039的应用、发现其中一个 ADC 测量值略高于预期值(AIO229)、并且引脚看起来为内部上拉。 我们将测量线性调频脉冲。

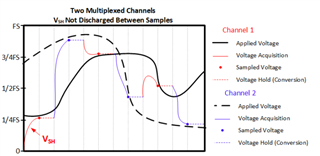

正在比较两个引脚( AIO229和 AIO248)以进行调试、检查后发现它们显然具有相同的配置( 无上拉、无反转、SYNC )、但 AIO229 显示了该"偏移"。

此外、使用测试仪 AIO229进行测量时、该值高于预期、 从电路断开 AIO229后、测量值返回到"预期"电压。

您知道这两个引脚之间是否有任何可能引发此问题的硬件差异吗? 或者、您可以预见任何可能导致此行为的特定配置吗?

此致、

马克·费雷尔

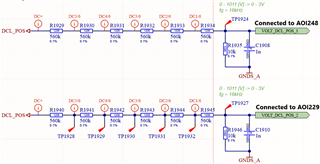

Ra = 300e、Rb = 1k、R1957 = 121k

Ra = 300e、Rb = 1k、R1957 = 121k