您好!

出于安全原因、我将着手测试闪存 ECC 逻辑功能、为此、我将遵循源代码 SDL_EX_FLASH_ECC_TEST 中的示例。

一切都运行良好、但我对测试期间的上下64位 SECDED 块的设置有一个疑问、这在我看来是没有道理的。

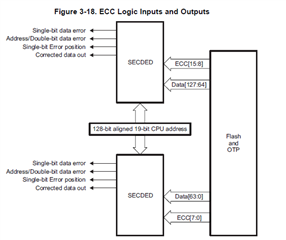

TRM 提到、一次只能测试一个 SECDED 模块(在两个工作在读取128位数据的低64位和高64位上的 SECDED 模块中)。

因此、我的理解是、在测试低块时、63:0范围内的一个单一位错误应该会 触发一个错误计数、但是如果一个单一位错误被注入到高块127:64、而在测试低块时、这个错误不应该触发一个错误计数。 但是、似乎确实如此。

我想了解、如果无论错误位位于128位数据中的什么位置、都检测到错误、那么使用两个块有什么作用。

测试上部和下部模块是否确实重要、或者只有一个测试足以证明 SECDED 模块的功能?

谢谢!

劳伦特