Other Parts Discussed in Thread: C2000WARE

主题中讨论的其他器件:C2000WARE

尊敬的专家:

我有一个关于邮箱数据接收的问题。

为了测试验收掩码、我修改了一个 back2bak 演示代码(C:\software\c2000ware\C2000Ware_4_03_00_00\device_support\f2806x\examples\c28\eCAN-back2back)。 我将邮箱30和邮箱31设置为接收邮箱、邮箱13和邮箱15设置为 发送邮箱。 邮箱30从邮箱13接收邮件。 邮箱31从邮箱15接收邮件。 我没有修改 InitECana()和 InitECanGpio() 。

这是代码

#define REC_MBOX31_MSGID_ID 0x784UL

#define REC_MBOX31_LOCAL_FILTER 0x0003FFFF

#define REC_MBOX30_MSGID_ID 0x785UL

#define REC_MBOX30_LOCAL_FILTER 0x0003FFFF

#define REC_MBOX_LAM_LAMI 0x80000000UL

#define REC_MBOX_MSGIN_AME 0x40000000UL

#define REC_MBOX30_LAM_REG ((REC_MBOX30_MSGID_ID<<18)&0x1FFFFFFF | REC_MBOX_LAM_LAMI)

#define REC_MBOX30_MSGID_REG ((REC_MBOX30_MSGID_ID<<18)&0x1FFFFFFF | REC_MBOX_MSGIN_AME)

#define REC_MBOX31_LAM_REG ((REC_MBOX31_MSGID_ID<<18)&0x1FFFFFFF | REC_MBOX_LAM_LAMI)

#define REC_MBOX31_MSGID_REG ((REC_MBOX31_MSGID_ID<<18)&0x1FFFFFFF | REC_MBOX_MSGIN_AME)

void main(void)

{

Uint16 j;

Uint16 i;

struct ECAN_REGS ECanaShadow;

InitSysCtrl();

InitECanGpio();

DINT;

InitPieCtrl();

IER = 0x0000;

IFR = 0x0000;

InitPieVectTable();

MessageReceivedCount = 0;

ErrorCount = 0;

PassCount = 0;

InitECana(); // Initialize eCAN-A module

//transmit setting

ECanaMboxes.MBOX13.MSGID.all = REC_MBOX30_MSGID_REG;// 0x9555AAAF;//

ECanaMboxes.MBOX15.MSGID.all = REC_MBOX31_MSGID_REG;// 0x9555AAAF;//

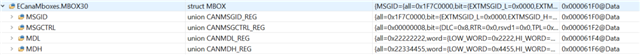

ECanaMboxes.MBOX30.MSGID.all = REC_MBOX30_MSGID_REG;// 0x9555AAAF;//

ECanaMboxes.MBOX31.MSGID.all = REC_MBOX31_MSGID_REG;//0x9555AAAF;//

ECanaRegs.CANMD.all = 0xC0000000;//CHANGE

ECanaMboxes.MBOX13.MSGCTRL.bit.DLC = 8;

ECanaMboxes.MBOX15.MSGCTRL.bit.DLC = 8;

ECanaMboxes.MBOX13.MDL.all = 0x22222222;

ECanaMboxes.MBOX13.MDH.all = 0x22334455;

ECanaMboxes.MBOX15.MDL.all = 0x11111111;

ECanaMboxes.MBOX15.MDH.all = 0x11223344;

ECanaRegs.CANTA.all = 0xFFFFFFFF; // Clear all TAn bits

ECanaRegs.CANRMP.all = 0xFFFFFFFF; // Clear all RMPn bits

ECanaRegs.CANGIF0.all = 0xFFFFFFFF; // Clear all interrupt flag bits

ECanaRegs.CANGIF1.all = 0xFFFFFFFF;

ECanaLAMRegs.LAM30.all = REC_MBOX30_LAM_REG;

ECanaLAMRegs.LAM31.all = REC_MBOX31_LAM_REG;

ECanaRegs.CANOPC.all = 0xC0000000; //change

//

EALLOW;

ECanaRegs.CANGIM.all = 0x00000000;

ECanaRegs.CANMIM.all = 0xFFFFFFFF;

ECanaShadow.CANMC.all = ECanaRegs.CANMC.all;

ECanaShadow.CANMC.bit.STM = 1; // Configure CAN for self-test mode

ECanaRegs.CANMC.all = ECanaShadow.CANMC.all;

EDIS;

ECanaRegs.CANMD.all = 0xC0000000;

ECanaRegs.CANME.all = 0xC000A000;

//

// Begin transmitting

//

for(;;)

{

//

// Set TRS for all transmit mailboxes

//

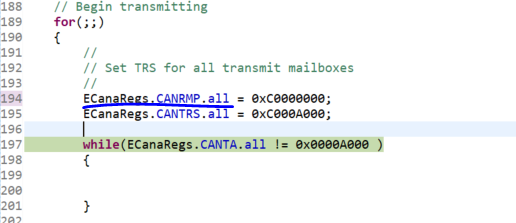

ECanaRegs.CANTRS.all = 0x0000A000;

while(ECanaRegs.CANTA.all != 0x0000A000 )

{

}

ECanaRegs.CANTA.all = 0x0000A000;

j=30;

mailbox_read(j);

}

}

void

InitECanaGpio(void)

{

EALLOW;

//

// Enable internal pull-up for the selected CAN pins

// Pull-ups can be enabled or disabled by the user.

// This will enable the pullups for the specified pins.

// Comment out other unwanted lines.

//

GpioCtrlRegs.GPAPUD.bit.GPIO30 = 0; // Enable pull-up for GPIO30 (CANRXA)

GpioCtrlRegs.GPAPUD.bit.GPIO31 = 0; // Enable pull-up for GPIO31 (CANTXA)

//

// Set qualification for selected CAN pins to asynch only

// Inputs are synchronized to SYSCLKOUT by default.

// This will select asynch (no qualification) for the selected pins.

//

GpioCtrlRegs.GPAQSEL2.bit.GPIO30 = 3; // Asynch qual for GPIO30 (CANRXA)

//

// Configure eCAN-A pins using GPIO regs

// This specifies which of the possible GPIO pins will be eCAN functional

// pins.

//

//

// Configure GPIO30 for CANRXA operation

//

GpioCtrlRegs.GPAMUX2.bit.GPIO30 = 1;

//

// Configure GPIO31 for CANTXA operation

//

GpioCtrlRegs.GPAMUX2.bit.GPIO31 = 1;

EDIS;

}

#endif

void

InitECana(void)

{

//

// Create a shadow register structure for the CAN control registers.

// This is needed, since only 32-bit access is allowed to these registers.

// 16-bit access to these registers could potentially corrupt the register

// contents or return false data.

//

struct ECAN_REGS ECanaShadow;

//

// Setup variables to initialize mailboxes to zero

//

int16 mboxCount;

volatile struct MBOX *Mailbox = (void *) 0x6100;

EALLOW; // EALLOW enables access to protected bits

//

// Configure eCAN RX and TX pins for CAN operation using eCAN regs

//

ECanaShadow.CANTIOC.all = ECanaRegs.CANTIOC.all;

ECanaShadow.CANTIOC.bit.TXFUNC = 1;

ECanaRegs.CANTIOC.all = ECanaShadow.CANTIOC.all;

ECanaShadow.CANRIOC.all = ECanaRegs.CANRIOC.all;

ECanaShadow.CANRIOC.bit.RXFUNC = 1;

ECanaRegs.CANRIOC.all = ECanaShadow.CANRIOC.all;

//

// Configure eCAN for HECC mode - (reqd to access mailboxes 16 thru 31)

// HECC mode also enables time-stamping feature

//

ECanaShadow.CANMC.all = ECanaRegs.CANMC.all;

ECanaShadow.CANMC.bit.SCB = 1;

ECanaRegs.CANMC.all = ECanaShadow.CANMC.all;

//

// Initialize all registers of the mailboxes to zero

// Some bits of MSGCTRL register come up in an unknown state.

// For proper operation, all bits (including reserved bits) of MSGCTRL must

// be initialized to zero

//

for(mboxCount=0; mboxCount<32; mboxCount++)

{

Mailbox->MSGID.all = 0;

Mailbox->MSGCTRL.all = 0;

Mailbox->MDH.all = 0;

Mailbox->MDL.all = 0;

Mailbox = Mailbox + 1;

}

//

// TAn, RMPn, GIFn bits are all zero upon reset and are cleared again

// as a matter of precaution.

//

ECanaRegs.CANTA.all = 0xFFFFFFFF; // Clear all TAn bits

ECanaRegs.CANRMP.all = 0xFFFFFFFF; // Clear all RMPn bits

ECanaRegs.CANGIF0.all = 0xFFFFFFFF; // Clear all interrupt flag bits

ECanaRegs.CANGIF1.all = 0xFFFFFFFF;

//

// Configure bit timing parameters for eCANA

//

ECanaShadow.CANMC.all = ECanaRegs.CANMC.all;

ECanaShadow.CANMC.bit.CCR = 1 ; // Set CCR = 1

ECanaRegs.CANMC.all = ECanaShadow.CANMC.all;

//

// Wait until the CPU has been granted permission to change the

// configuration registers

//

do

{

ECanaShadow.CANES.all = ECanaRegs.CANES.all;

} while(ECanaShadow.CANES.bit.CCE != 1 ); // Wait for CCE bit to be set

ECanaShadow.CANBTC.all = 0;

//

// The following block is for 90 MHz SYSCLKOUT.

// (45 MHz CAN module clock Bit rate = 1 Mbps)

// See Note at end of file.

//

ECanaShadow.CANBTC.bit.BRPREG = 2;

ECanaShadow.CANBTC.bit.TSEG1REG = 10;

ECanaShadow.CANBTC.bit.TSEG2REG = 2;

ECanaRegs.CANBTC.all = ECanaShadow.CANBTC.all;

ECanaShadow.CANMC.all = ECanaRegs.CANMC.all;

ECanaShadow.CANMC.bit.CCR = 0 ; // Set CCR = 0

ECanaRegs.CANMC.all = ECanaShadow.CANMC.all;

//

// Wait until the CPU no longer has permission to change the

// configuration registers

//

do

{

ECanaShadow.CANES.all = ECanaRegs.CANES.all;

} while(ECanaShadow.CANES.bit.CCE != 0 );// Wait for CCE bit to be cleared

//

// Disable all Mailboxes

//

ECanaRegs.CANME.all = 0; // Required before writing the MSGIDs

EDIS;

}

#endif // endif DSP28_ECANA

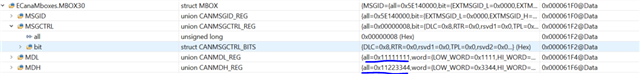

如果设置正确、邮箱30应该接收到 0x22222222和 0x2233455。 邮箱30应接收0x11111111 和0x11223344。

但当我调试时、mailbox30有时会收到 0x22222222和0x2233455 、有时会收到 0x11111111 和0x11223344 。 似乎邮箱30接收到两个发送邮箱的消息。

但是、如果我注释代码 ECanaRegs.CANOC.all = 0xC0000000;、问题就不会再发生了。

您能帮我找出哪里出了问题吗?

除了我想要一个关于接受屏蔽的演示、因为我认为这个代码中的设置可能是错误的。 我在 SPRA876B 中提到的 c2000ware_1_00_01_00 中进行了下载、但在 C:\ti\c2000\C2000Ware_1_00_01_00\device_support\F2833x\examples 中找不到 CAN_LAM 示例。 您能举个例子吗?

代码位于附件中。

感谢您的帮助!!

此致

奇田市