主题中讨论的其他器件:TMDSCNCD280039C、 TMDSHSECDOCK

尊敬的德州仪器团队:

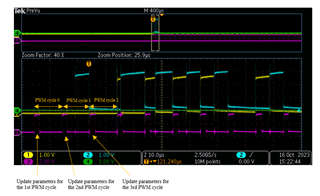

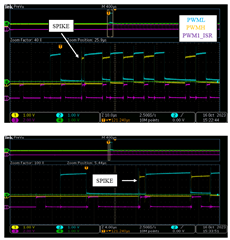

目前、我正在开发用于控制 LLC 转换器的软件。 如您所知、在启动期间、前几个 PWM 周期需要非对称 PWM、而后需要对称互补 PWM 模式。 在随附的 图中、 前6个 PWM 周期显示了 LLC 启动过程中的 PWM 图形示例。

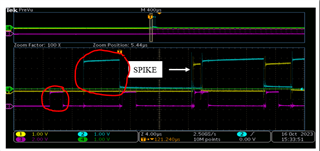

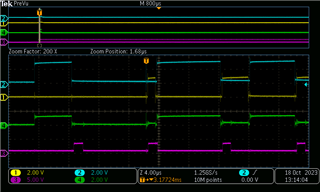

图1:启动过程的 PWM 模式。

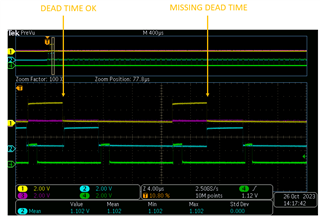

以下是前六个 PWM 模式的一些注意事项:

第1个 PWM 周期–只应开启低侧 MOSFET。 高侧 MOSFET 关断。 PWM 在互补模式下不工作。

第2个 PWM 周期–低侧和高侧 MOSFET 都应关断。 PWM 在互补模式下不工作。

第3个 PWM 周期–低侧和高侧 MOSFET 在互补模式下运行、其中高侧 MOSFET 的占空比小于低侧 MOSFET 的占空比。

第4个 PWM 周期-低侧和高侧 MOSFET 在互补模式下运行、这时高侧 MOSFET 的占空比与低侧 MOSFET 相比更小、但低侧和高侧占空比之间的比率现在发生了变化。 增加高侧 MOSFET 的占空比、降低低侧 MOSFET 的占空比。

第5个 PWM 周期-低侧和高侧 MOSFET 采用对称 PWM 模式在互补模式下运行-两个 PWM 信号的占空比均为50%。

第6个 PWM 周期-低侧和高侧 MOSFET 采用对称 PWM 模式在互补模式下运行–两个 PWM 信号的占空比均为50%。

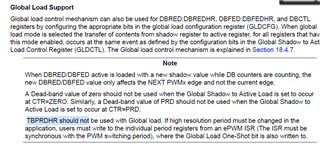

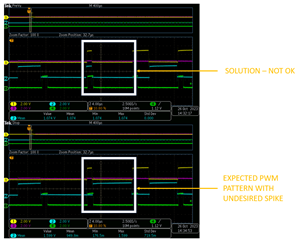

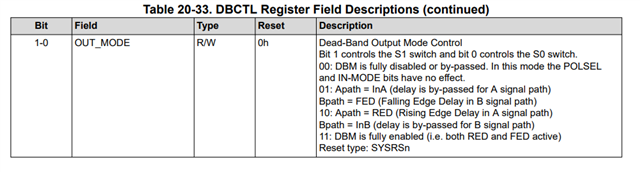

我附上了 用于测试启动 PWM 模式的 main.c 文件。 在 PWM 中断内部、PWM 参数会针对每个新的 PWM 周期进行更新。 为了使一切都透明且同步、应选择全局加载选项以同时更新所有需要的寄存器。 出现的问题是在第3个 PWM 周期开始时、PWM 周期开始时会出现较小的尖峰。 这不是由干扰引起的尖峰、也不是由不良的测量设置引入的尖峰。 我假设发生这种情况是因为死区子模块在第二个 PWM 周期中被旁路、而在第三个 PWM 周期中被启用。 但我不明白为什么启用了全局加载。 您能告诉我发生这种情况的原因以及如何解决尖峰问题吗? 这种行为是不可接受的。