大家好、

CMPSS 基准电压配置为使用 VDDA 且未启用 VDAC。 当 VDAC/B3引脚处于悬空状态时、为什么它会干扰 CMPSS3比较器并导致比较器结果不正确?

CMPSS 信号远未达到设定的阈值、但会提前触发保护(阈值设置为在2.9V 处触发、但实际的输入信号仅为2.1V)。

CMPSS1/3/4同时使用、但只有 CMPSS3会提前触发保护、另外两个通常会触发、没有问题。 CMPSS3的输入信号为 A3引脚。

此致、

赞讷

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

大家好、

CMPSS 基准电压配置为使用 VDDA 且未启用 VDAC。 当 VDAC/B3引脚处于悬空状态时、为什么它会干扰 CMPSS3比较器并导致比较器结果不正确?

CMPSS 信号远未达到设定的阈值、但会提前触发保护(阈值设置为在2.9V 处触发、但实际的输入信号仅为2.1V)。

CMPSS1/3/4同时使用、但只有 CMPSS3会提前触发保护、另外两个通常会触发、没有问题。 CMPSS3的输入信号为 A3引脚。

此致、

赞讷

Hadi、您好!

CMPSS3基准电压配置为使用 VDDA。 但当让 VDAC/B3悬空时、它会感染 A3。

您能解释一下吗? 这里有同样的问题:(+) TMS320F280049:ePWM 给 ADC 引脚 B3、VDAC 带来了干扰- C2000微控制器论坛- C2000 ︎ 微控制器- TI E2E 支持论坛

此致、

赞讷

尊敬的 Zane:

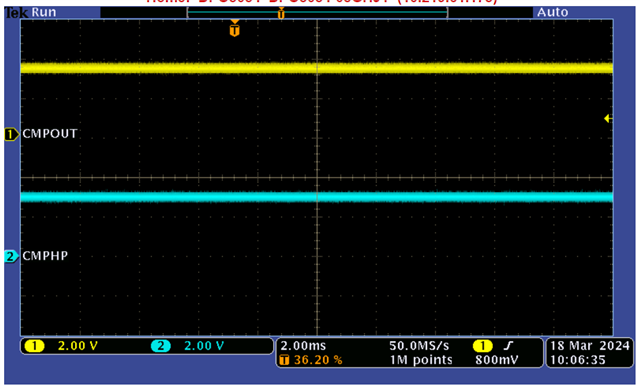

我试图在最终重现该问题、但 CMPSS3运行良好。

在这里、您可以看到在 B3/VDAC 悬空的情况下进行测试的结果、而我将2.91V 提供给 A3并且内部 DACH 使用 VDDA 并设置为3600。 您可以看到、输出变为高电平。

当施加2.88V 的信号时、输出变为低电平:

客户是否对引脚 A3使用了任何 RC 滤波器? 请分享有关其电路信号调节的更多信息。

此致、

哈迪

Hadi、您好!

感谢您的确认! 客户电路板上有很多噪音。

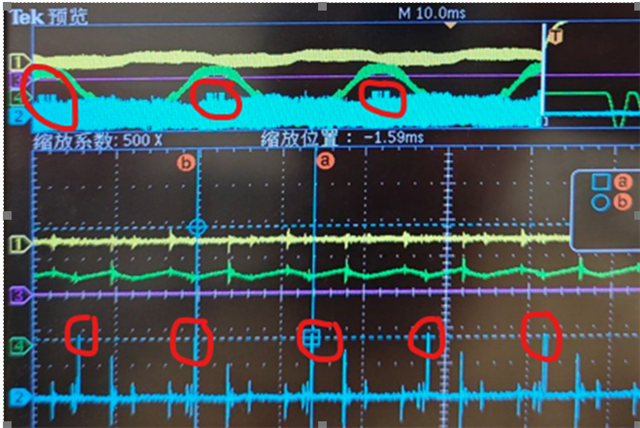

CMPSS3早期触发问题、虚假触觉不是连续触发、而是脉冲触发。 通常、连续触发对于阈值来说是真;可能是由于干扰等因素造成的脉冲形式会导致比较器结果不正确。

如下所示、触发器位于红色圆圈处。 在输入电流达到峰值时和 MOS 管开关时会发生错误触觉。

因此、我们自行判断:MOS 管的开关状态会干扰 B3/VDAC、 进而干扰 CMPSS3的基准电压(例如、假设 CMPSS 设置3.3V 的基准电压、干扰会导致实际基准电压为2.3伏、从而提前触发保护)。

通道2:CMPOUT

CH4:电流枪测试的输入电流

我们是否有比较器模块的内部架构图?

干扰是否可能影响 CPMSS3多路复用器上的其他引脚、导致引脚电压超过3.3V。 接地的 VDAC/B3引脚可有效解决此问题。

此致、

赞讷

Hadi、您好!

请参阅以下内容、它不仅发生在 F280039上、还发生在 F280049上。

请帮助我们找到答案! 非常感谢!

TMS320F280049:ePWM 使 ADC 引脚 B3、VDAC 发生干扰- C2000微控制器论坛- C2000 ︎ 微控制器- TI E2E 支持论坛

此致、

赞讷

尊敬的 Zane:

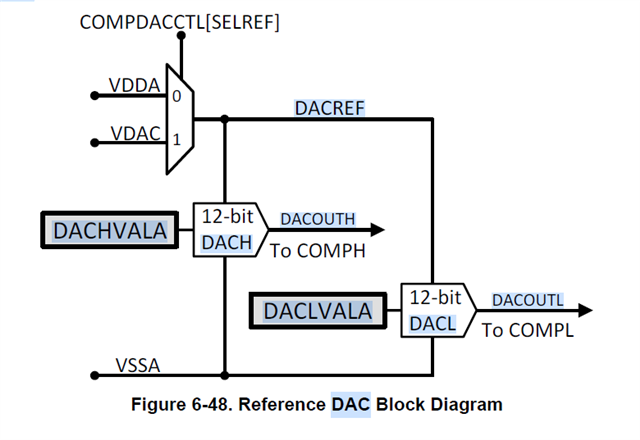

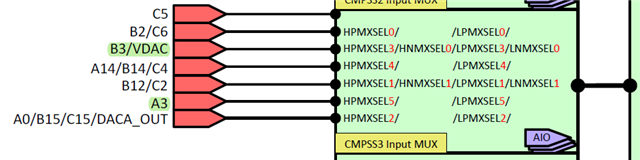

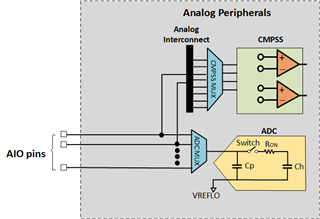

此处您可以找到模拟外设互连的简化原理图。 更详细的模拟子系统图如 TRM 中的图12.1所示。

此外、CMPSS 模块的基准 DAC 如图16.3所示。 如您所见、比较器基准来自 VDDA 或 VDAC、并可使用寄存器 COMPDACCTL[SELREF]进行选择 。 在您的情况下、需要使用 VDDA。 但是、从您提供的结果中可以清楚地看出、由于串扰、电路中开关活动的噪声会耦合到比较器的输入引脚、并会发生误触发。

以下是一些抑制串扰的快速设计提示:

1) 减少允许并行运行两条线的长度。 信号宽度至少要留出三倍的间距是一条很好的经验法则。 确保在可能的情况下具有实心的返回路径。 减小信号与地之间的间隔、可确保信号具有良好的返回路径。 此处提供了一篇 TI 文章、其中详细介绍了减少串扰的不同注意事项和 PCB 布局技巧。 本文提供了可帮助您减少遇到的串扰问题的适用信息。

2) 低通滤波器模式非常适合用于信号中存在瞬时干扰或高频噪声的重复采样应用。

此致、

哈迪

Zane,

在此处提到的主题中、客户在其 ADC 中断中读取 B3/VDAC 引脚、但您的客户并非如此。 您不是在读取 B3/VDAC 引脚。

模拟多路复用器和 ADC 之间是采样保持电路。 因此、每次将多路复用器从 ON 信号切换到另一个信号时、都需要将旧电平耦合到新信号。 所需的充电时间取决于驱动器阻抗。

以下是我的问题:

1) 1)客户对 A3引脚使用的 RC 值是多少?

2) ADC 读数使用哪些通道?

3) 3)请客户启用引脚 B3/VDAC 上的内部上拉电阻、并让我知道比较器的行为。 默认情况下、该引脚用作模拟引脚、且 GPIO 处于高阻抗状态。 GPyAMSEL 寄存器用于配置这些引脚的数字或模拟操作。 它们需要使用以下函数在 AIO242上内部启用上拉电阻:

此致、

哈迪