主题中讨论的其他器件:C2000WARE、 TMDSCNCD28P65X

尊敬的专家:

我的电路板可以独立启动、并且可以正常运行。

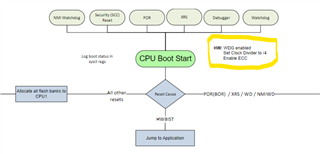

但是、当 CPU1 - WDT 复位发生复位或 CPU2上发生 TRIG CPU1 - NMIWDT ISR 超时复位时、CPU1无法复位成功。

我参考了 TI 示例代码- CPU2 WDT 复位和 CPU1 NMIWDT ISR TRIG 以复位 CPU2可以成功。 所以、我认为 CPU2复位是可以的。

另一个 TI 示例代码- CPU1 WDT ISR 与我的应用不匹配、这个示例代码集 WDT 模式是 ISR 模式、因此我没有进行测试。

顺便说一下,当我复位 CPU1 ,然后使用 JTAG 连接下载代码和重新启动,我可以看到 WDT REG - WDRSn (看门狗复位标志)打开。 我认为 CPU1 WDT 功能正常、但重新启动失败。

因此、我想知道如何解决 CPU1 WDT 复位或 NMIEWDT 复位的问题?

谢谢。

B.R.

螺栓