Other Parts Discussed in Thread: C2000WARE

Thread 中讨论的其他器件:C2000WARE

工具与软件:

我想了解如何配置 CM 时钟、因为当前时钟仅是25 MHz 而不是125 MHz。

CPU1使用位字段库进行编程、CM 使用 driverlib 进行编程。

我使用 CPU 计时器0验证 CM 内核的时钟频率。 此代码基于定时器示例"timer_ex1_cputimers"。 周期设置为500us (499 * 125个周期)。

CPUTimer_setPeriod (CPUTIMER0_BASE、125*499);

ISR 切换 GPIO。 PWM 频率应为1kHz、但仅为200Hz。 由此我得出结论、CM 时钟为25 MHz。

在下一步中、我使用 CPU1的 ePWM1模块验证了 PLLSYSCLK 的结果、CPU1时钟为200 MHz

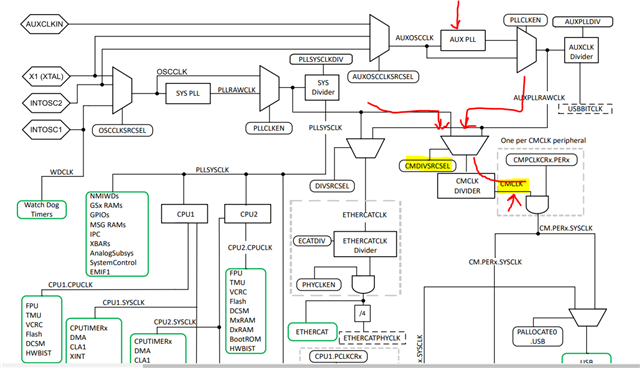

在《TMS320F2838x 技术参考手册》(SPRUII0C)的第3.7章中、图3-6展示了时钟系统。 CMCLK 可由 PLLSYSCLK 或 AUXPLLRAWCLK (选择 PLLSYSCLK)供源、并且只能由"CMCLK 偏差器"(寄存器 ClkCfgRegs.CMCLKCTL.CMCLKDIV)进行偏差。 使用该寄存器、PLLSYSCLK 可以达到/1 /2 /3 /4 /5 /6 /7 /8。 如何将 CM 配置为在 PLLSYSCLK 为200 MHz 时运行 Witz 125 MHz? 其可能的偏差包括200 MHz、100 MHz、66.7 MHz、50 MHz、40 MHz 可支持33.3 MHz、28、6 MHz 和25 MHz。

我的代码和使用的值都是从以下示例中得出的:

ClkCfgRegs.CMCLKCTL.ALL =~0xF0U |(((0x1 & 0x07U)<< 0x05U)|((0x1 & 0x01U)<< 0x04U));

因此 CMCLKDIV 为7 (对于/8)。 这意味着 CMCLK = 200 MHz /8 = 25 MHz。 当 CMCLKDIV = 0时、CMCLK 为200 MHz。 我认为时钟速率不能高于125 MHz。

我的理解问题在哪里?