主题中讨论的其他器件:Tina-TI、 SysConfig、 TMS320F28P659DK-Q1、

工具与软件:

您好!

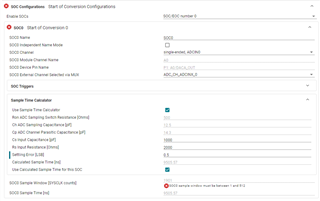

我将尝试读取两个不同 ADC 输入上的同一模拟信号。

我使用的引脚是 GPIO205

我将会读取 C4和 B28上的信号。

对于两个分辨率为12位的 ADC、读数都由 PWM1 @300kHz 触发。

C4和 B28都会返回相同的值。

问题是、当我读取 C4和 B28时、该值与仅读取 C4的情况不同。

差值约为20/4096位。

如果我在不同的 PWM (PWM3、仍@300kHz)上触发 B28的读取:

C4和28都会返回相同的值、本例与我只读取 C4的情况相同。

因此、对于我的应用、我已经使用不同的触发器解决了问题、但我想了解原因。

另请考虑、我还有其他 由 PWM1触发的 ADC。

使用同一 PWM 可以触发多少 ADC? 该问题是否与频率相关?

其他限制?

谢谢