工具与软件:

我目前正在使用3个 AD9695 (即 A、B 和 C)和1个 lmk04828时钟芯片调试开发板。 LMK04828芯片在级联零延迟双环路模式下运行、并且 sysref 会持续生成。 在 Verilog 程序中、使用相同的 JESD204 RX IP 内核(对于 SYSREF 始终开启、则为默认的 SYSREF)。 通过调整 declk 和 sysref 的延迟、我能够在同一内核时钟周期内对齐来自 RX IP 内核的 rx_tvalid 输出。

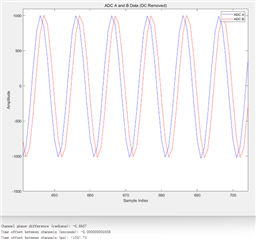

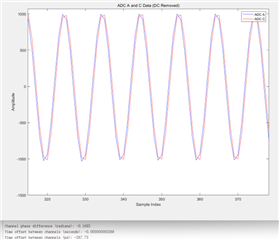

然而、根据结果、交流采样数据是同步的、但 AB 不是同步的。 下图展示了对同一正弦波进行 AB 和 AC 采样的结果。

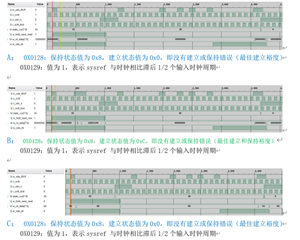

这是否与 AD9695寄存器(0x128、0x129)中 sysref 的建立和保持状态有关? 或者、是否存在多芯片同步方案的任何参考?