工具与软件:

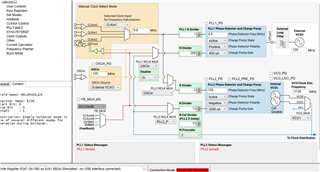

为了确定 PLL 是否已锁定、我进行了以下设置:

我想通过 Status_LD1和 Status_LD2观察 PLL1和 PLL2的锁定状态。

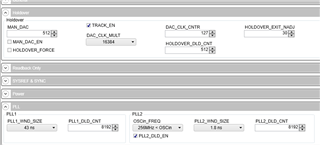

PLL 的配置如下:同时使用两个 PLL 并在外部使用一个120MHz VCXO:

实际机器测试已发现状态 LD2为高电平、状态 LD1为低电平。

关闭外部输入时钟源(600kHz)后、状态 LD2和状态 LD1的状态没有变化。

正如预期的那样、当有一个时钟输入时、状态 LD2和状态 LD1应该被发出以表示 PLL1和 PLL2被锁定。 当没有时钟输入时、状态 LD2和状态 LD1应为低电平。

但事实并非如此。 我可以问一下我的配置有问题的地方吗?

此外、我想问是否可以使用状态 LD2或状态 LD1来观察是否仅使用一个 PLL 锁定?