Other Parts Discussed in Thread: ADC12QJ1600

主题中讨论的其他器件:ADC12QJ1600

工具与软件:

大家好、团队成员:

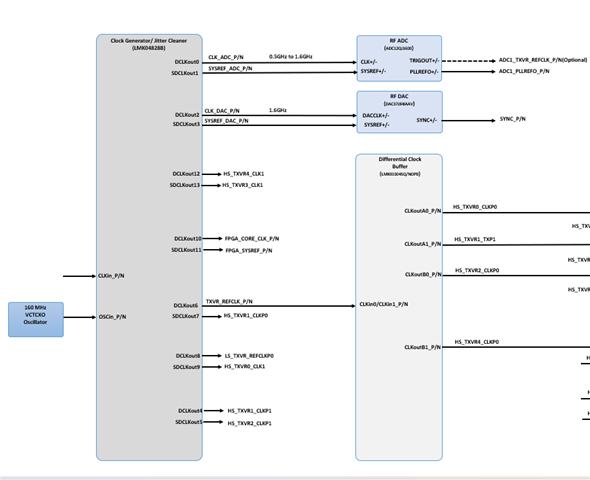

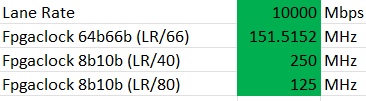

我想将 LMK04828B 时钟发生器、 ADC12QJ1600AAVQ1:模数转换器(ADC)和 DAC37J84IAAV:数模转换器(DAC)与 Altera Agilex 5器件相连。

我想知道时钟要求是什么、例如 ADC 和 DAC 的器件时钟和参考频率? 以及 FPGA 参考时钟需要支持的时钟频率范围。

此致、

列表