Other Parts Discussed in Thread: LMK00334, LMK00804B, LMK1C1104, LMK00304

主题中讨论的其他器件: LMK1C1104、 LMK00304、LMK00334、LMK00804

工具与软件:

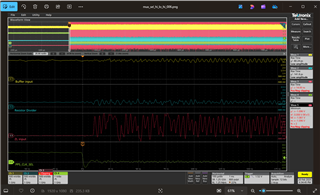

我发现了一个问题、即器件的输入端会产生噪声、输出变得无法使用/不稳定。

由于 LVCMOS 和 DIFF 输入上的1Hz (1 PPS)输入均设置为 CMOS 输入、因此当 CLK_SEL 从1更改为0时、我会看到所有输入和输出上的噪声。

当它为1时、两个输入看起来都正常、并且输出遵循所选的输入。 我看到了问题、那就是当我将 CLK_SEL 更改为0时、

我应该寻找什么来帮助确定看到此错误的原因。 如果不使用任何信号驱动 LVCMOS 输入、我也会看到此问题。

所示。 缓冲器输入= LVCMOS 输入) 电阻分压器是差分输入的 P half。 ZL_INPUT 是 LMK008804 PPS_CLK_SEL 的输出、是选择输入。