工具与软件:

您好!

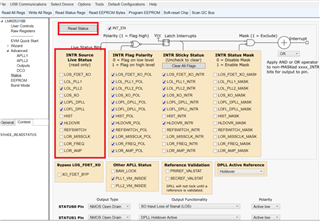

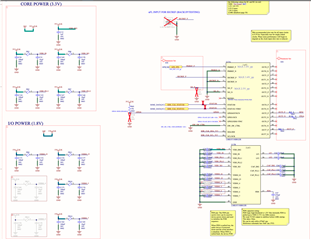

我们在定制 PCB 中使用 LMK05318B、但在将我们的配置刷写到 EEPROM 后未获得任何时钟输出。 请来自 TI 的人查看我们的 TICS Pro 配置和硬件原理图、特别是要查找那些突出、可能妨碍我们从 LMK05318B 获取任何信号输出的问题。

我们已经以相同的配置对 LMK05318BEVM 进行了编程、并获得预期的时钟输出、因此我们认为 TICS 配置不是问题。 我们还基于数据表的原理图、因此应该有最小的差异。

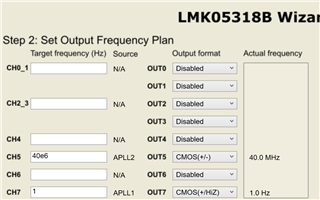

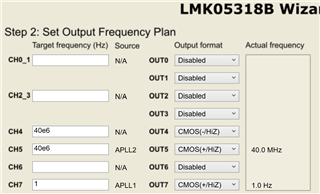

相关时钟输入/输出:

XO 输入:24MHz LVCMOS

优先级:1PPS LVCMOS

Out5:40MHz 低电压互补金属氧化物半导体(LVCMOS)(_P 和_N 上都有+输出)

OUT7:1PPS (仅限 LVCMOS、+输出)

有关优化 OUT5的相关问题:以下输出配置中、TI 会建议哪些配置?

e2e.ti.com/.../2727.config.tcse2e.ti.com/.../eeprom_5F00_instructions.txt

e2e.ti.com/.../2727.config.tcse2e.ti.com/.../eeprom_5F00_instructions.txt