请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:LMK05318B 工具与软件:

您好!

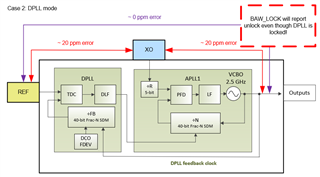

根据 TICS Pro (v1.7.7.10)中的注释、我看到了在使用 DPLL 时禁用 BAW 频率锁定检测的建议。 您能否确认这是正确的?

(我想这是因为当 DPLL 处于活动状态时、它负责2.5GHz BAW 振荡器的控制? 这意味着出于某种原因不需要 BAW 频率锁定检测?)

产生混淆的原因是1PPS 默认配置启用了 DPLL 以及 BAW 频率锁定检测。 我一直假设、对于任何设计而言、此1PPS 默认配置都是安全/验证的起点。 如果情况不是这样、则需要关注。

谢谢你。