主题:TDC7200中讨论的其他器件

工具/软件:

您好:

TDC 参数在 DPLL/整个系统中似乎相当重要、但我尚未完全理解。 在使用 PRIREF 1PPS 时、TI 是否有关于选择 TDC 的任何信息/指导? 具体来说、1PPS 的默认值(1PPS)是否优于最大26MHz?

提前感谢。

-

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具/软件:

您好:

TDC 参数在 DPLL/整个系统中似乎相当重要、但我尚未完全理解。 在使用 PRIREF 1PPS 时、TI 是否有关于选择 TDC 的任何信息/指导? 具体来说、1PPS 的默认值(1PPS)是否优于最大26MHz?

提前感谢。

-

尊敬的 Quin 和 Jennifer:

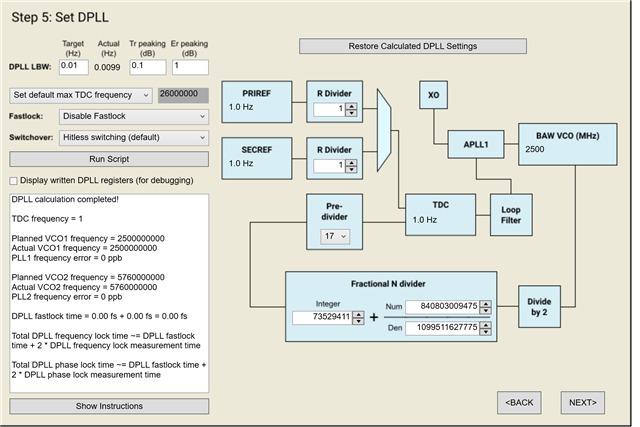

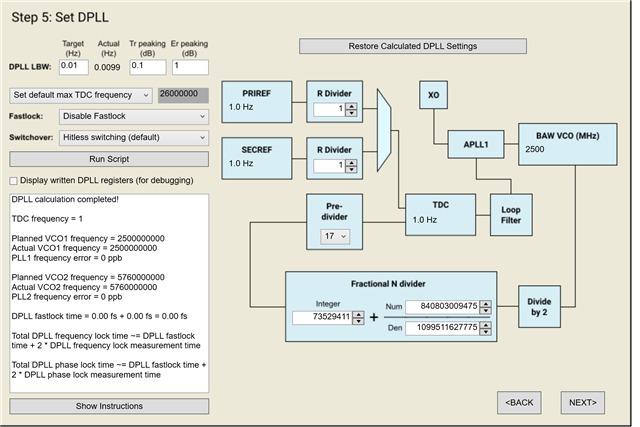

我想最好提一下、我们有两个不同的参数、即 TDC 速率和 TDC 计数频率。

我对 TDC 块的理解。

TDC (计数)频率越高(默认为26MHz)、相位测量就越精细、因此最终的相位噪声越低

但它的缺点是捕获范围较低。 REF 的容差必须更接近 XO、才能在有限的 TDC 计数器中捕获。

我说这是错误的方式的目的,因为 XO 的观点。

然后、在1PPS 的情况下、我们的 TDC 速率为1Hz。

每秒一次测量不应干扰 DPLL 环路带宽来避免欠采样。

建议使用 DPLL TDC 速率的1/100。

也许有一点偏离主题、请简短查看 TDC 内部的 TDC7200数据表。

此致、

Octo