请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:LMK05318B 工具/软件:

您好:

我对 TICS 中的一些 LMK05318B 参数/我在数据表中看到的一些参数还有几个问题:

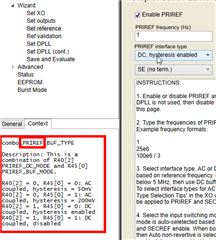

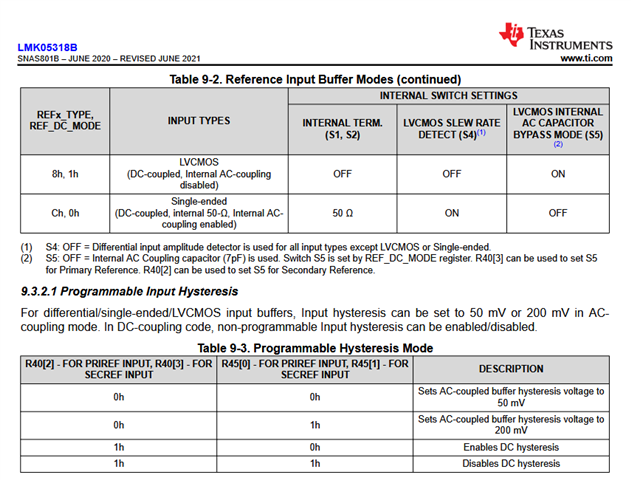

1)您能帮助解释在基准输入缓冲器模式下 LVCMOS 和单端之间的区别吗? 此外、使用单端/LVCMOS 信号时、REF_DC_MODE 寄存器(R40[3])是否设置在 TICS GUI 中的某个位置?

2)我不理解 DPLL 频率。 使用锁定检测精度(ppm)参数。 特别是、它如何影响 DPLL 锁定或不锁定?

非常感谢