工具/软件:

您好:

我的客户通过增加目标 DPLL LBW 来减少器件的重新同步时间、但他们 担心相位噪声和稳定性、因为 它们会增加重新同步频率。 我们是否有任何方法来表征它会如何变化? 它们从5Hz 开始、然后提高到100Hz。

我们是否有资源可以模拟或提供有关这个问题的指导? 主要思路是缩短锁定时间(使用更高的环路滤波器 BW)、并希望评估是否有任何负面影响。

谢谢!

Owen

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具/软件:

您好:

我的客户通过增加目标 DPLL LBW 来减少器件的重新同步时间、但他们 担心相位噪声和稳定性、因为 它们会增加重新同步频率。 我们是否有任何方法来表征它会如何变化? 它们从5Hz 开始、然后提高到100Hz。

我们是否有资源可以模拟或提供有关这个问题的指导? 主要思路是缩短锁定时间(使用更高的环路滤波器 BW)、并希望评估是否有任何负面影响。

谢谢!

Owen

尊敬的 Owen:

您是否知道客户使用的 TDC 频率? 此外、您是否知道它们在近端偏移处是否有任何相位噪声要求?

通常、来自基准的相位噪声将在低于 DPLL LBW 的偏移处占主导地位。 如果基准频率相对干净、或客户不关心近端偏移处的相位噪声、那么将 DPLL LBW 提高到100Hz 之类的频率通常没有太多缺点。 如果他们只对12kHz -20MHz 集成相位噪声感兴趣、那么 DPLL LBW 不会对性能产生任何重大影响。

在 TICS Pro 中生成配置时、向导将在"Set DPLL"页面上运行脚本后估算锁定时间。 如果 DPLL LBW 不适合给定的 TDC 频率、它还将发出警告。

此致、

Connor

您好、Connor、请查看以下客户反馈:

e2e.ti.com/.../LMK05318B_5F00_Config_5F00_04102024_5F00_manual-holdover.tcs

TDC 频率为50kHz、请参见下面的配置:

时钟输出相位噪声要求(156.25Mhz)如下:

因此、未指定低于10kHz 的相位噪声。 我在此处附加了 LMK 配置文件、仅使用 SECREF。

谢谢!

Owen

尊敬的 Owen:

感谢您发送 CONFIG。 在这种情况下、如果近端相位噪声不是问题、那么 DPLL LBW 可以达到100Hz。 我们 在数据表的第9.2.2节中提供了一些设置 LBW 的指南:

"编程的 DPLL 环路带宽(BWDPLL)应低于以下所有值:

DPLL TDC 速率的1/100

2. APLL1环路带宽(典型值为1kHz 至10kHz)

3.最大 DPLL 带宽设置为4kHz"。

以100Hz LBW 运行此配置的 DPLL 脚本后、估算的相锁时间约为1.1秒。 如果只使用其中一个基准、我建议禁用未使用的输入。 这样、脚本就不需要考虑输入频率之间的最大公共因素、这样就可以实现更高的 TDC 频率。 通常、TDC 频率越高、锁定时间就越短。 例如、禁用 PRIREF 会将 DPLL 快速锁定时间从约900ms 缩短至60ms。 如果您有任何其他问题、请告诉我。

此致、

Connor

尊敬的团队:

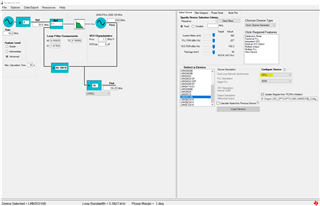

我仍然很难使用 PLLatinum Sim 工具仿真 LMK05318B (主要是 DLF 100Hz 与5Hz)、附件是实际的配置文件。

TicsPro 显示了 DPLL 配置、如下所示:

当我使用 PLLatinum Sim 工具加载 TicsPro 生成的相同 TCS 文件时、我获得了以下配置:

您可以看到 DPLL 配置与 TicsPro 的配置不匹配、这可能是什么问题?

e2e.ti.com/.../LMK05318B_5F00_Config_5F00_04102024_5F00_cfg_5F00_mga_5F00_BAWDisabled_5F00_OscNo50ohm.txte2e.ti.com/.../LMK05318B_5F00_Config_5F00_04102024_5F00_cfg_5F00_mga_5F00_BAWDisabled_5F00_OscNo50ohm.tcs

谢谢、

Owen

尊敬的 Owen:

我刚刚对此进行了测试、似乎 PLLatinumSim 没有正确地从.tcs 文件导入 DPLL 配置。 我建议通过加载 LMK05318B DPLL 器件并键入振荡器频率、设置 TDC N 分频器等来手动进入配置 您能否试用附加的.sim 文件并查看它是否有效? 我还继续、针对100Hz 的目标 DPLL LBW 重新计算了 PLLatinumSim 中的环路滤波器设置。

此致、

Connor