工具/软件:

尊敬的团队:

在我们的原理图中、我们使用 LMK04828B、我们旨在将 CLKIN0直接路由到 SYSREF 路径、类似地、将 CLKIN1直接路由到外部 VCXO 路径。 这意味着 输入 应直接连接到时钟分配路径。 虽然我们尝试了此配置、但未实现预期的结果。 您能否解释一下实施此设置的正确步骤?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具/软件:

尊敬的团队:

在我们的原理图中、我们使用 LMK04828B、我们旨在将 CLKIN0直接路由到 SYSREF 路径、类似地、将 CLKIN1直接路由到外部 VCXO 路径。 这意味着 输入 应直接连接到时钟分配路径。 虽然我们尝试了此配置、但未实现预期的结果。 您能否解释一下实施此设置的正确步骤?

您好 Sarathi、

您能否分享您尝试实现的内容的方框图或时钟树?

在大多数情况下、使用 TICSpro 对配置有帮助。

如果您使用的是自己的定制电路板而不是 LMK04828EVM (评估板)、则还可以将配置导出为.txt 文件、以供驱动程序参考

此拓扑后面的内容可以有效地进行配置。

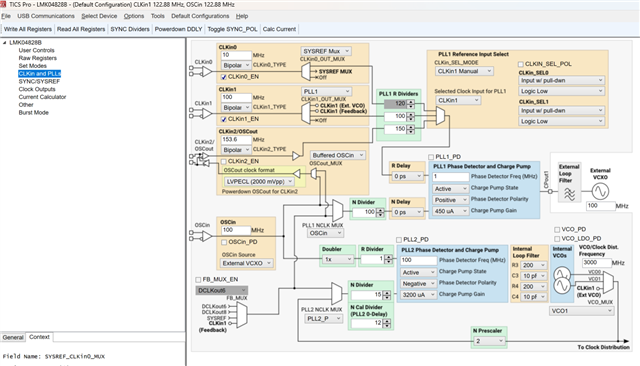

此处、CLKIN0路由到 SYSREF_MUX、CLKin1路由到 PLL1、以驱动外部 VCXO。 在本示例中、我假设您要驱动100MHz VCXO。

您还可以通过将 CLKin1_OUT_MUX 设置为"Fin"来缓冲 CLKin1的输入、这只会绕过 PLL2、并使器件在缓冲模式下运行。 此时、您在 CLKin1拥有的任何信号都将连接到时钟分配路径。

对于 SYNC/SYREF 页面、您需要将 SYSREF_CLKin0_MUX 设置为"从 CLKin0"、这会将 CLKin0上的 SYSREF 信号直接发送到 SYSREF 分配路径。

此致、

Vicente