工具/软件:

您好、

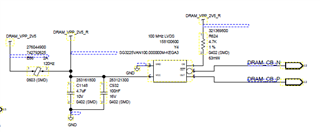

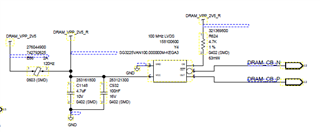

我在设计中使用了 LMK1D1204 IC、如下所示

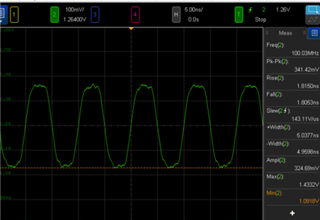

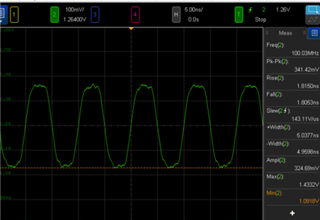

测量 SG3225的输出时钟、似乎可以。

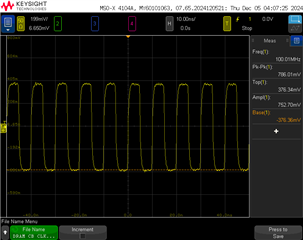

但是、LMK 缓冲器的输出时钟似乎 是非单调的、在使用差分探头时看起来也比较棘手。

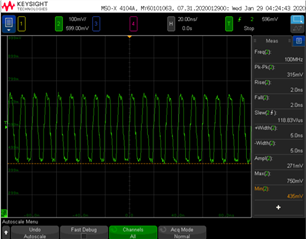

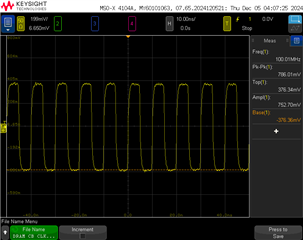

使用"P"上的单端探头和连接到电路板接地的接地夹进行测量

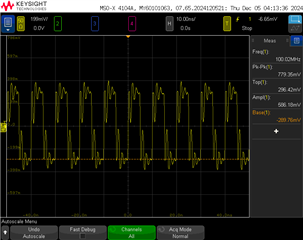

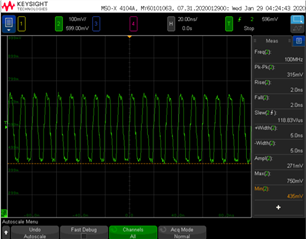

使用"P"和"N"之间的差分探头进行测量

您能告诉我如何进行调整吗?

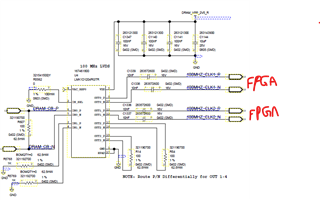

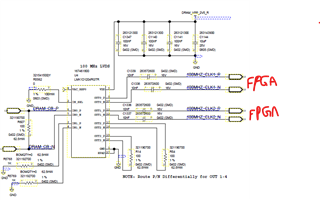

LMK 缓冲器的时钟输出进入 Virtex UltraScale+ FPGA、在那里我们使用 DIFF_SSTL12标准。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具/软件:

您好、

我在设计中使用了 LMK1D1204 IC、如下所示

测量 SG3225的输出时钟、似乎可以。

但是、LMK 缓冲器的输出时钟似乎 是非单调的、在使用差分探头时看起来也比较棘手。

使用"P"上的单端探头和连接到电路板接地的接地夹进行测量

使用"P"和"N"之间的差分探头进行测量

您能告诉我如何进行调整吗?

LMK 缓冲器的时钟输出进入 Virtex UltraScale+ FPGA、在那里我们使用 DIFF_SSTL12标准。

尊敬的 Vincente:

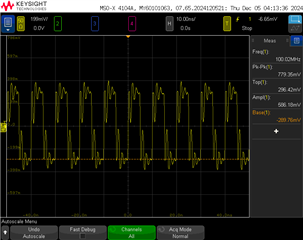

在电阻器(在 FPGA 附近)处进行探测有所帮助。 波形看起来更好。

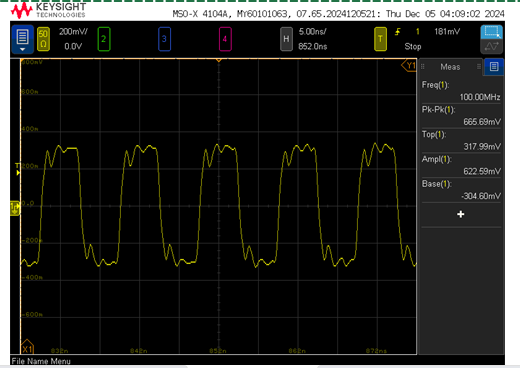

上面是使用 DIFF 探头捕获的波形。 由于 Vpk-pk 为665mV、我们是否可以说差分电压(Vdiff)为665/2 = 332.5mV?

此外、根据之前分享的单端探头测量值、如果我们将 Vmax 视为750mV、我们可以说共模电压= VMAX-(Vdiff/2)= 750 -(332.5/2)= 583.75mV 吗?

如果没有、请分享如何根据这些波形查找共模电压。

谢谢你

Nandini

您好:Nandini、

是的、我们总是想在 Rx 附近进行探测、而不是在 T 线的中间、否则您最终会像以前一样看到奇怪的反射。

如果此测量是在交流耦合电容器后完成的、则无法计算此信号的 Vcm。

交流耦合电容器阻止了直流失调电压。

您需要在耦合电容器之前进行探测、以查看 VCM/VCM VOL 的位置、从此处查看 VOH VOH + VOL)/2

此致、

Vicente