主题中讨论的其他器件: CDCI6214、

工具/软件:

您好的团队、

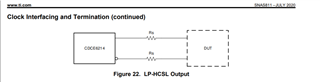

我们认为 在我们的 PCIe 第3代或第4代应用设计中使用 CDCE6214RGET 器件、CDCE6214将支持 LP-HCSL 输出时钟技术。

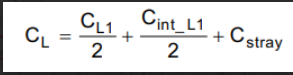

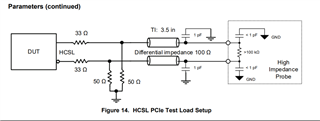

CDCE6214RGET 数据表中未介绍 RS 端接电阻器阻值。

我们又有一个 PCIe 第3代器件支持 CDCI6214器件、但不建议将此器件用于新设计。

但在该数据表中、提到了 PCIe 测试负载设置的端接电阻值。

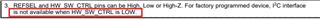

您能否提供 CDCE6214RGET (LP-HCSL)的 PCIe 测试负载设置的端接详细信息、而 CDCE6214RGET 器件将有两个 EEPROM 页面(0、1)、我们将在我们的设计中使用 EEPROM 第0页。

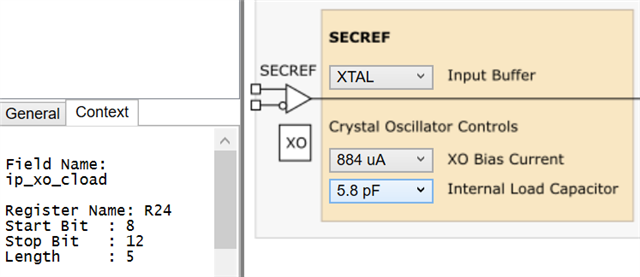

即出厂编程值、将反映在输出上。 我们想知道 EEPROM 第0页中的默认出厂编程频率值?