工具/软件:

大家好!

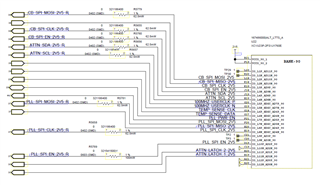

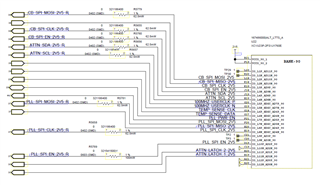

我们正在使用 LMX2582RHAT 我们也看到了一些改进 以及 PCB 布局技术 SPI 信号 (CLK、CS、SDI) 上的电压。 这些信号由 FPGA 驱动。

以下是当前驱动强度设置:

PLL_SPI_EN:12mAPLL_SPI_CLK:12mAPLL_SPI_MOSI:12mA

我们想知道:

- 该过冲和下冲是否在可接受的限值内?

- 如果没有、您可以建议如何减少这些损耗

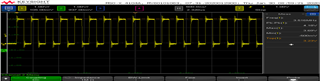

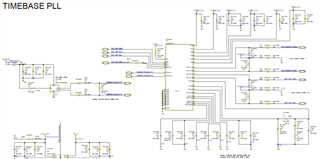

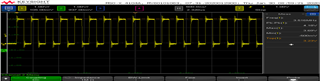

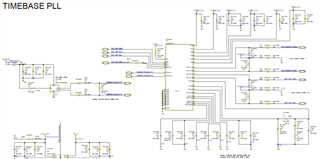

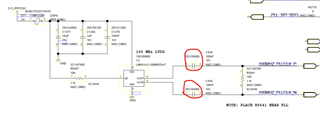

我附上了 SPI 时钟的信号捕获图和相关原理图以供参考。

谢谢

Sakthi

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具/软件:

大家好!

我们正在使用 LMX2582RHAT 我们也看到了一些改进 以及 PCB 布局技术 SPI 信号 (CLK、CS、SDI) 上的电压。 这些信号由 FPGA 驱动。

以下是当前驱动强度设置:

PLL_SPI_EN:12mA PLL_SPI_CLK:12mA PLL_SPI_MOSI:12mA 我们想知道:

我附上了 SPI 时钟的信号捕获图和相关原理图以供参考。

谢谢

Sakthi

你(们)好

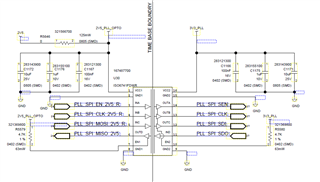

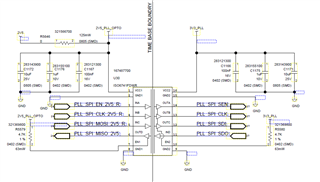

在我们的设计中、我们将电容器放置在电阻器基准设计之前:C929、C930。 我们在 100MHz clk 中仍然没有看到任何问题。 移动电容器是否需要在电阻器的另一侧。

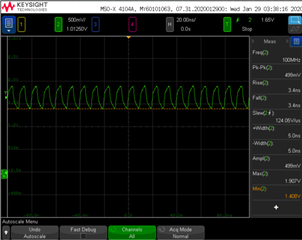

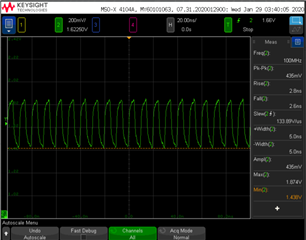

我附上了设计和波形的图像以供您参考。

'100MHz_PLLCLK_P

100MHz_PLLCLK_N

我们更改了 SEN 引脚的电阻值。 我们增加了一个 33 欧姆的电阻器、而不是 0 欧姆、但与 0 欧姆相比没有太大的差异。 我们是否需要调整 FPGA 的驱动强度?