工具/软件:

大家好:

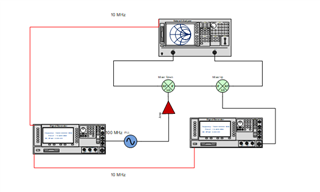

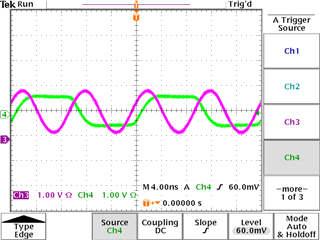

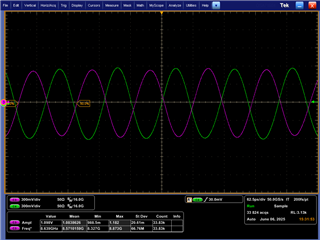

我目前正在从事一个涉及 LMX2820 的设计。 此设计的主要目标是实现基准信号和输出之间的 0º Ω 相移。 目标是使用多个 LMX2820 器件并确保所有输出信号与主基准同步。

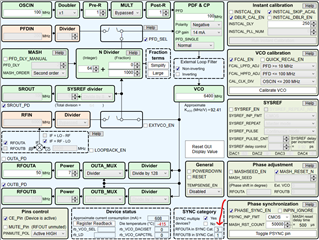

为此、我们计划使用基于运算放大器 (OA) 的有源滤波器。 根据数据表、最好使用三阶滤波器而不是二阶滤波器、主要用于按照建议放置电容器。

我们面临的主要挑战是滤波器设计本身。 我们使用了 PLLatinum 工具并分析了不同的选项。 但是、我们没有找到有关整个拓扑的输出相位的任何信息、并且我们不确定如何保证 0º Ω 的相移。

如果您对设计此滤波器有任何见解或提供合适的实现方案示例、都将非常有帮助。 我们还愿意使用不同的运算放大器模型来实现滤波器、因此如果您有任何建议、它也会很有帮助。

提前感谢您的时间和帮助!

此致、

日本