Thread 中讨论的其他器件: LMK5B33216、 USB2ANY

工具/软件:

之前:

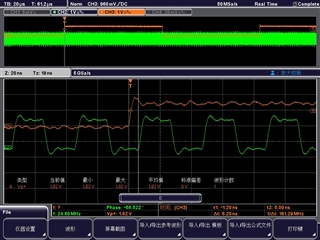

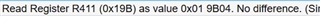

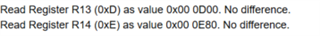

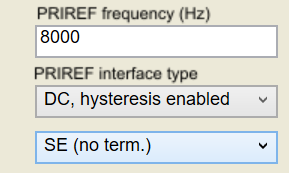

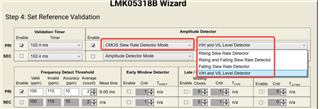

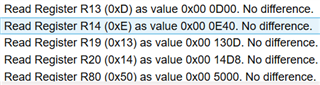

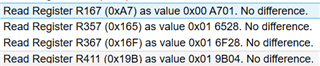

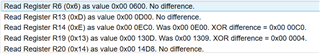

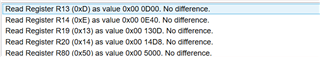

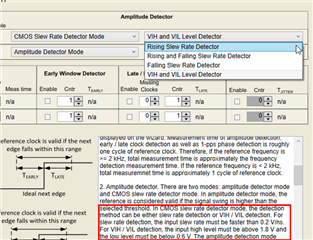

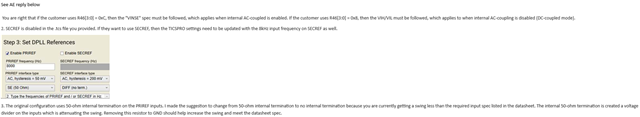

我们工程中使用的 05318b 用作抖动清除器芯片、输入 ref clk = 8kHz、输出 out7 24.576MHz、输入模式配置为直流模式、相应的寄存器 reg40 0x07、寄存器 reg46 0x1c 指示单端(内部端接 50Ω)。 由于是直流模式、05318b 芯片的引脚 PRIREF_P 约为 1.3V、非 1.8V 有可能被识别为低电平。 但输入和输出的时钟相位同步、因此在音频通道中没有噪声。

之后:

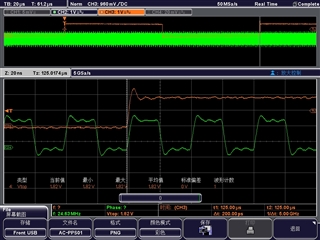

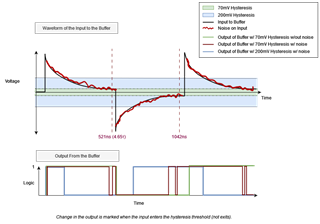

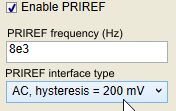

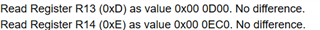

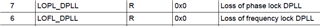

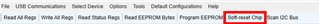

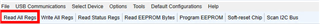

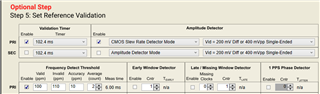

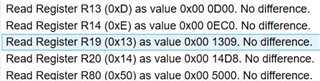

我们根据 TI 工程师的建议配置进行配置、将寄存器 reg40 修改为内部耦合 0x03 AC、将 reg46 修改为 0x18 以指示 CMOS。 芯片的 PRIREF_P 引脚为 1.8V、但我们发现输入和输出的时钟相位未同步、这也会导致我们最终输出的音频通道上产生噪声。

问题:

我们想知道 在将直流模式更改为交流模式时、为什么输入和输出的时钟相位不同步、以及如何解决该问题并更改时钟相位以实现同步。