主题中讨论的其他器件: LMX2592

工具/软件:

尊敬的团队:

我的客户已评估 LMX2572。

作为一项持续的挑战、PLL 的锁定时间已成为一个问题。

以下是他们正在考虑的问题。

・LMX2572

- FOSC: 40.96MHz 带部分辅助-> VCOcal 是 98us

在其测量仪器中实施的应对测量变化的措施(PLL 输出信号的杂散?) AS

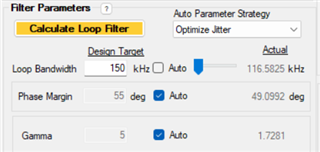

KPD:0.625mA、MASH 顺序:第 4 个

他们希望这个时间小于 100us、包括没有完全辅助的锁定时间。

・更改了 Fosc

- Fosc:带部分辅助功能的 81.92MHz ->总计 108.3us

MASH 顺序:FVCO 小于 3604.5GHz 时的第三个环路增益变化误差(在 KPD 1.25mA 中解析)

・LMX2592 上的快速校准

- Fosc: 40.96MHz VCOcal30us 共 90.9us

如果 tjey 具有与 LMX2572 相同的环路滤波器和相同的 KPD、则会得到环路增益变化误差

他们正在考虑这一点。

您能给我一些建议吗?

至于完全辅助、如果可能、他们希望在不使用完全辅助的情况下实现小于 100us 的 PLL 锁定时间。

因为;

-用作测量仪器的测量信号。

-这是因为他们不知道在他们的工厂提供固定的辅助价值的所有问题。

他们思考;

-该值随温度的变化而变化。

-它也取决于芯片的个体差异。

以此类推。

因此、它们需要开启并使用 VCOcal 本身。

此致、

二宫幸史