工具/软件:

TI、您好:

我对 LMX2594 的相位噪声性能有疑问。

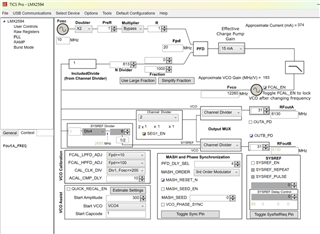

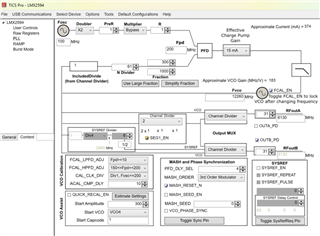

下图分别显示了案例 1、案例 2 和案例 3 的 GUI 界面设置。 案例 1 与案例 3 的区别在于、Fosc 是 10MHz 和 100MHz。 情况 2 是情况 1(倍频器:X2 和泵充电 15mA) 的)的微调结果。

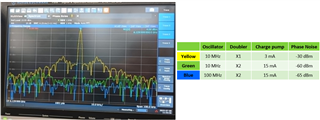

最后一张图显示了 SA 的测量结果、黄线(情形 1)是这三种情况中的最坏情况。 由于实际应用需要 Case1 设置、因此我 想知道 在倍频器固定为 X1 且电荷泵固定为 15mA 时、是否还有其他设置可以降低噪声。

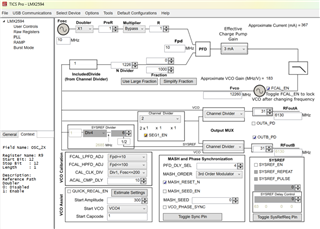

案例 1:

案例 2:

案例 3:

感谢你的帮助。

Brian Chiou