Thread 中讨论的其他器件:TLV3801-Q1、 SN65LVELT23、LM27762、 CD74HC4053、TMUX4053 、 TMUX1072、 TMUX1574、 TLV3801

工具/软件:

我的目标是将两种类型的信号引入器件中

- 单端+/–1V 正弦波、例如来自 OCXO 10 或 100MHz 的正弦波

- LVCMOS 2.5 - 3.3V 选通脉冲(例如 1PPS 脉冲)

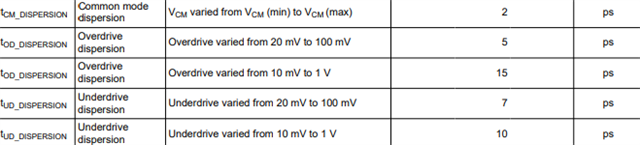

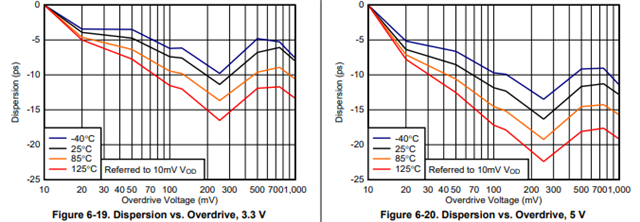

器件的前端需要处理这两种类型的信号以及适当的端接(例如连接到 GND 的 50 Ω 电阻器或可选高阻态)、并将它们转换为适合作为 TDC 的启动/停止信号的快速上升沿。 前端电路应尽可能保持输入信号的阈值交叉时序。 如果输入端存在逐周期抖动、则应在输出端保留。

用户可以在电子控制下、在正弦脉冲和 LVCMOS 脉冲输入之间重新配置前端。 即前端不必能够在输入类型之间无缝切换、但任何重新配置都必须能够使用电子信号进行、而不需要手动切换或插入/拔出。

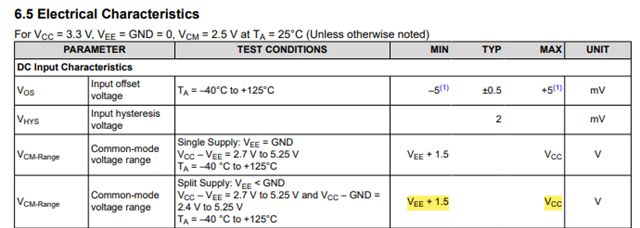

我最初计划使用一个 直接连接到输入信号的模拟比较器(如 TLV3801-Q1)、然后使用 LVDS 至 TTL(如 SN65LVELT23) 来 为 TDC 生成启动/停止脉冲。 IN-引脚可通过一个模拟开关连接至 GND、以提供交流正弦信号、并通过一个 1.65V 精密基准提供选通脉冲。 VEE 将保持在–1.65V、因此 VCC - VEE < 5.25V

然后、我阅读“使用时钟缓冲器进行正弦波 — 方波转换“应用手册 SNAA411、其中建议通过连接到 LMK1C110x 时钟缓冲器输入端的去耦电容器和偏置分压器、从正弦输入端生成高保真 LVCMOS 时钟输出。 这种方法需要更多的电路才能使其适用于 3.3V 选通脉冲。 是否有建议的方法为 LMK1C110x 创建灵活的前端电路以处理直流和交流耦合单端信号?

鉴于需要额外的电路来处理这两种输入信号情况、您可以告知这两种方法中的哪一种可能代表输出端输入信号的阈值/过零时序?

是否有比这两种方法更好的前端架构来从我所述的输入信号生成 TDC 启动/停止信号?