“TLC3555-Q1、 TLC3555 主题中讨论的其他器件“

工具/软件:

PCN 20231130002.1 是“针对特定器件采用合格工艺技术、裸片修订版本、数据表更新和其他组装地点/BOM 选项的 RFAB 认证“。 受影响的器件为 TLC555C、TLC555I、TLC555Q、但不为 TLC555-Q1。

预期的性能差异是什么?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具/软件:

PCN 20231130002.1 是“针对特定器件采用合格工艺技术、裸片修订版本、数据表更新和其他组装地点/BOM 选项的 RFAB 认证“。 受影响的器件为 TLC555C、TLC555I、TLC555Q、但不为 TLC555-Q1。

预期的性能差异是什么?

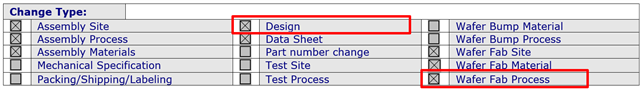

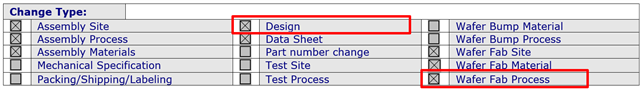

关键变更包括设计和晶圆制造厂工艺;这意味着更改器件原理图和所用元件。 这是一个重大变化。 这些变化使器件更好。 这对新设计很有利、并且对于主要关注点始终相同的旧设计来说、这可能会带来麻烦。

下面列出了 PCN 之后更好的器件、其顺序更有可能在应用中产生负面影响。

这些是 PCN 之后自然产生的和意想不到的副作用、但效果更好

其他差异

项目符号 1:传播延迟更低、因此稳定的振荡器将具有更高的输出频率

此图表显示了 PCN 之后基于 PCN 之前原始观测频率的应快得多。 电源电压会影响频率增加量。 较低的电源电压会产生更多的变化。 1kHz 时的频率增加很小、当原始频率超过 100kHz 时、频率显著增加。

请注意、理想的 A 稳态频率基于这些简单的低电平和高电平时间公式。 频率为 1/(tH + TL)。

理想的公式不包括传播延迟 (tPLH、tPHL)、它会导致斜坡电压更大。 下面是更准确的公式。 频率为 1/(TC (H)+ TC (L))。

PCN 会减少传播延迟、因此频率会更快、但仍低于理想公式。 使用下表了解基于电源电压的延迟。 对于 3V 和 5V 之间的电压、根据 3V 和 5V 条目进行内插。 对于 5V 和 15V 之间的电压、根据 5V 和 15V 条目进行内插。

|

PCN 之前 |

左侧 TPD |

TPD HL |

|

3V |

320ns |

250ns |

|

5V |

250ns |

200ns |

|

15V |

160ns |

160ns |

|

PCN 之后 |

左侧 TPD |

TPD HL |

|

3V |

88ns |

74ns |

|

5V |

80ns |

67ns |

|

15V |

56ns |

47ns |

要点 3、添加了启动电路以实现更可靠的启动

PCN TLC555 之前没有启动电路。 它自然地启动了。 在极少数情况下、偏置电路无法上电。 PCN 之后添加了启动电路、以确保在所有工艺和极端温度下都能正常启动。

但是、较大的振幅和快速压摆率 VDD 干扰可能会导致 PCN 之后的输出状态意外改变。 PCN 之前的版本不受影响。 数据表清楚地表明需要适当的旁路电容。 如果遵循此建议、则不应发生较大或快速的 VDD 干扰。 线路上方的干扰(更大或更快的压摆率)可能会导致不正确的输出信号。

要点 4、PCN 修复了 THRES 可以覆盖 TRIG 的缺陷

只有少数应用同时施加 TRIG 和 THRES、同时强制 CONT 为低电压。 这些应用可能具有不同的输出状态、因为 PCN 之前具有真值表缺陷、而 PCN 之后没有此缺陷。

依赖此缺陷的应用程序将不再工作。 在图表中、TRIG 为低电平、THRES 为高电平、两者均有效。 根据真值表、TRIG 应覆盖 THRES、从而使输出为高电平。 当 CONT 电压为低电平时、输出可能为低电平、与真值表相冲突。

图表数据中的迟滞是一个输出可能为高电平或低电平的区域、具体取决于序列或同时施加 TRIG 和 THRES、并且 CONT 为较低电压。

用于恢复以前应用程序结果的短期解决方案

TLC555-Q1 可用作 SOIC 封装的替代可订购器件。 它不受第一个 PCN 的影响。 它以低至 2V 的 VDD 运行、但数据表中的规格最小值为 5V。 未来的第二个 PCN 将替换所有 TLC555、包括 TLC555-Q1;它将接近原始器件替换版本、但并非完全如此。 阈值覆盖触发器缺陷将不会位于第 2 个 PCN 中。

用于保持适当应用结果的长期解决方案。

在对外部元件进行 TLC3555-Q1 性能调优后、可以使用 TLC3555-Q1。 TLC3555-Q1 没有设计/工艺 PCN、因此始终(迄今为止)采用相同的工艺和设计。 当 DISCH 大于 VDD 或 THRES 应覆盖 TRIG 缺陷时、TLC3555-Q1 将不起作用。 未来的商业级 TLC3555 将发布、其典型性能与 TLC3555-Q1 相同、但没有汽车级认证。