主题中讨论的其他器件: LMX2594、 LMK04832

工具/软件:

尊敬的 TI 专家:

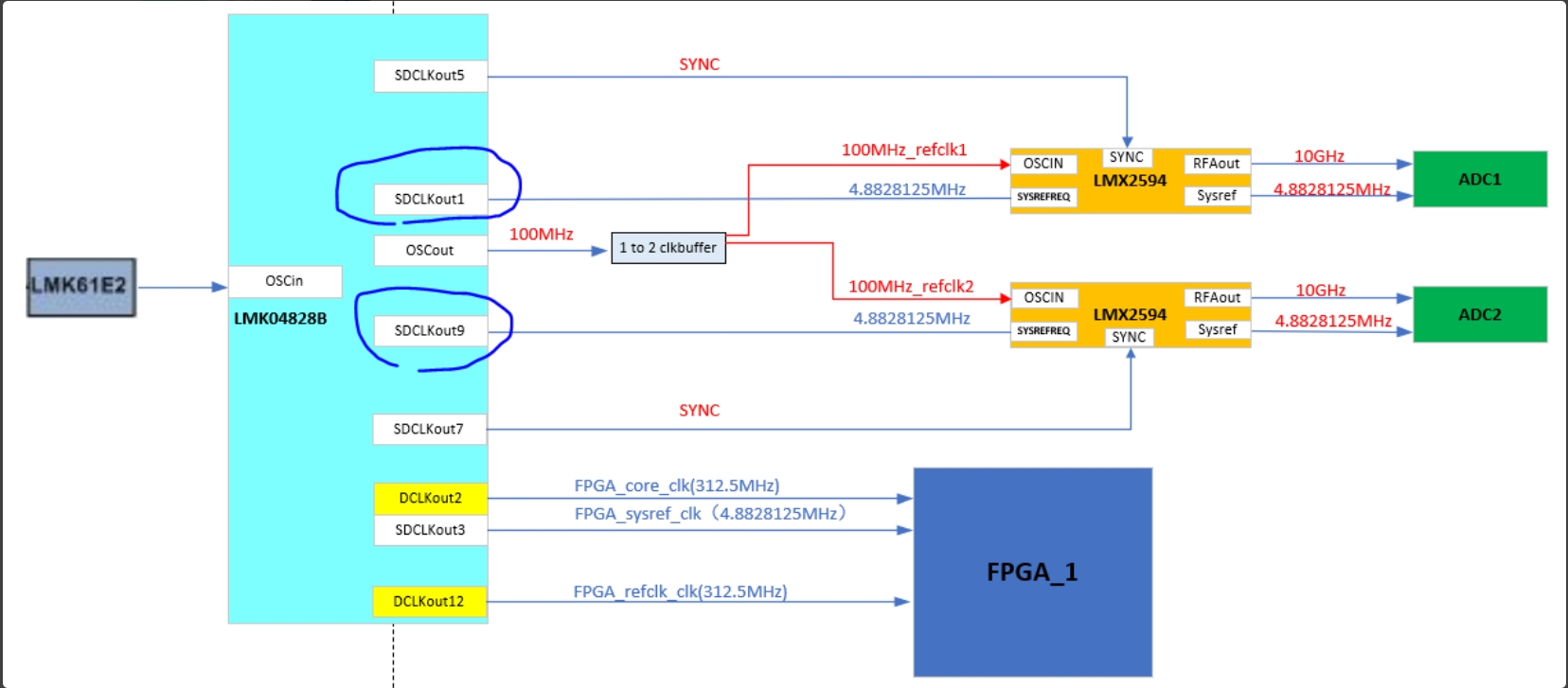

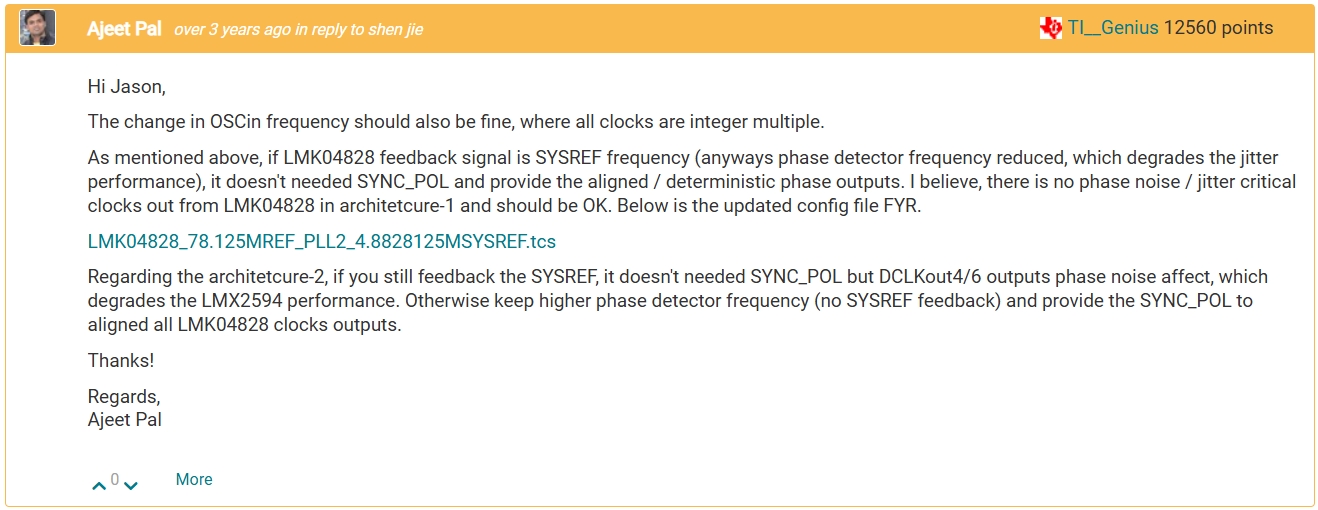

浏览 https://e2e.ti.com/support/clock-timing-group/clock-and-timing/f/clock-timing-forum/1168146/lmx2594-how-to-align-sysref-clock-between-lmx2594-when-need-to-realize-multi-chip-synchronization/4419573?tisearch=e2e-quicksearch&keymatch=lmx2594%20sysref 网页时、我看到有一位专家使用 ZDM 模式提供了参考.tcs 项目、其中输入时钟为 78.125MHz 、输出时钟为 4.8828125MHz、 如图 1 所示。 但是、我注意到在文档“多时钟同步“中、ZDM 使用规则:

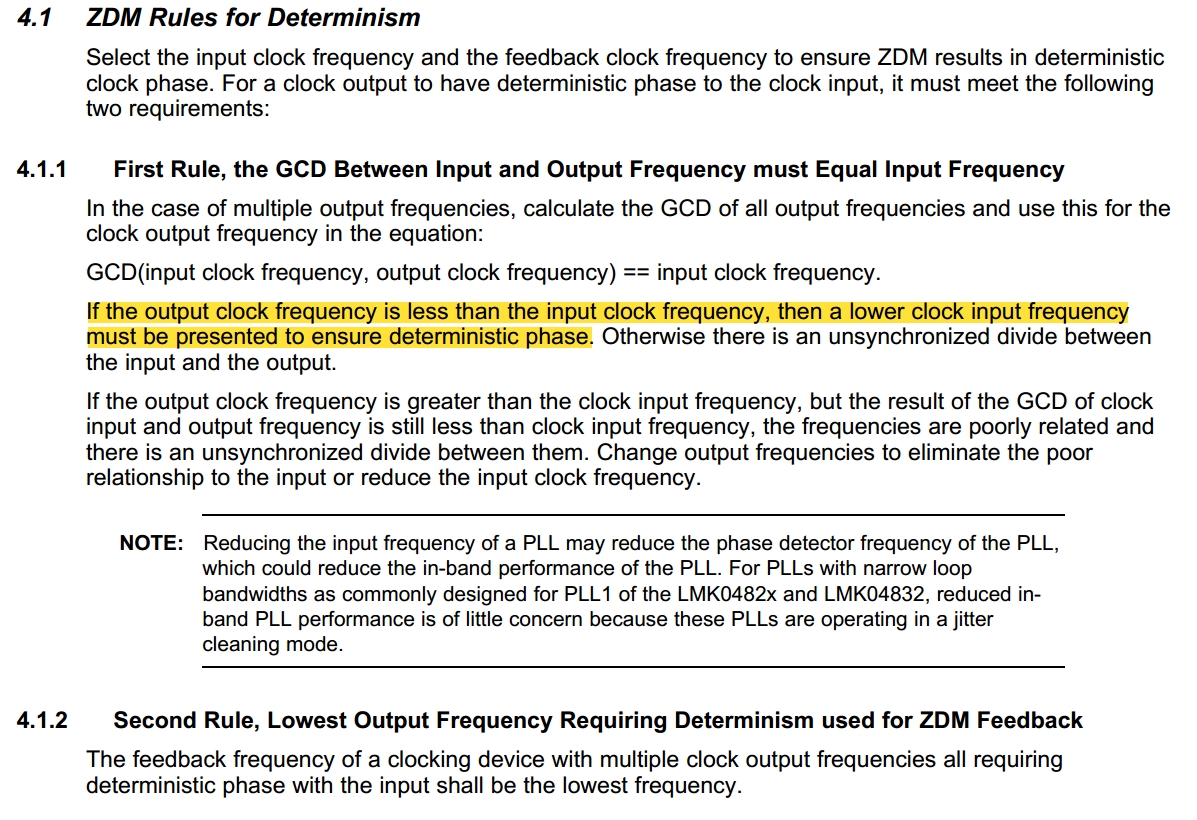

“如果输出时钟频率小于输入时钟频率、则必须呈现较低的时钟输入频率以确保确定性相位。“(如图 2 所示)。

因此、我想问:使用 ZDM 时、输出时钟频率低于输入时钟频率是否可以接受?

图 1.

图 2.

此致。