主题中讨论的其他器件: CDC6C、 LMH1983

工具/软件:

您好、

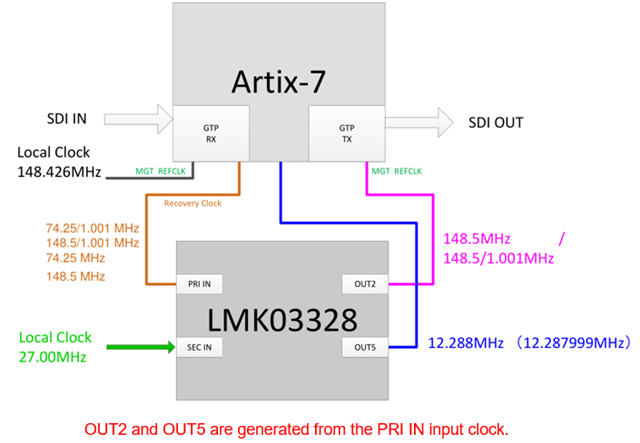

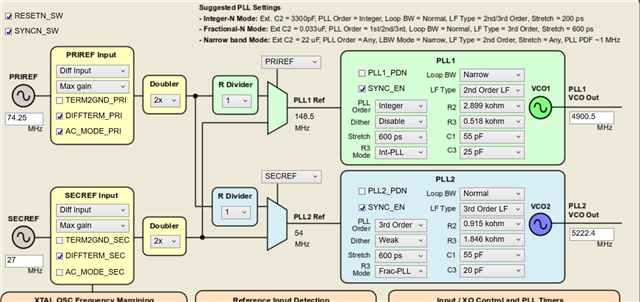

我们目前正在考虑将您的器件 LMK03328 与 Xilinx Artix-7 FPGA 结合使用。

该系统按如下方式运行:

-

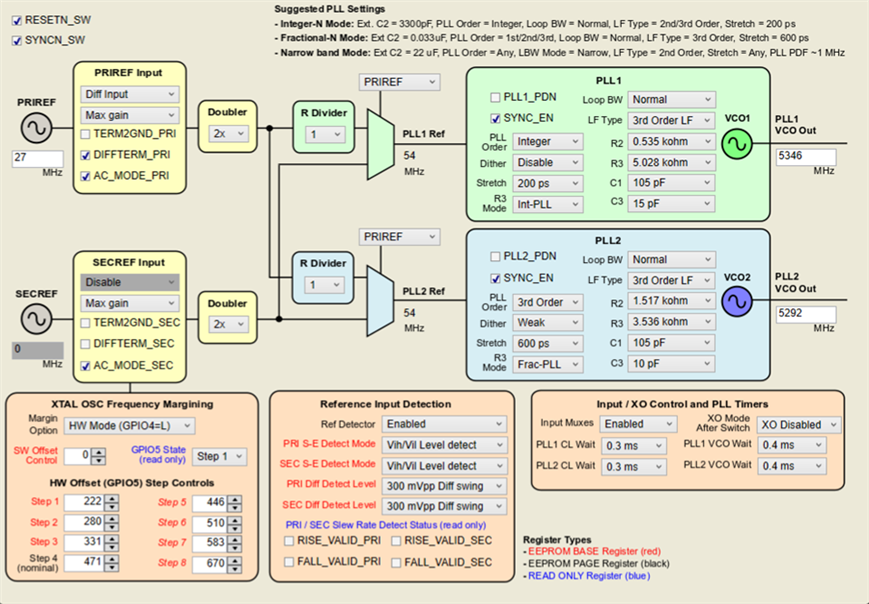

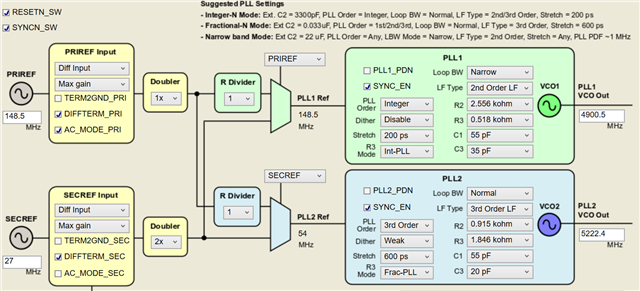

输入时钟(恢复时钟):74.25MHz、74.25/LSB 1.001MHz、148.5MHz、1.001MHz

-

LMK03328 用于抖动消除和时钟生成。 输出时钟为:

-

148.5MHz 或 148.5/REFCLK(用作 1.001MHz 7 GTP 发送器的 REFCLK)

-

12.288MHz(用于音频时钟)

-

我们知道、Artix-7 上的 GTP 收发器对 REFCLK 具有严格的相位噪声/抖动屏蔽要求。

您能否证实在该配置中使用 LMK03328 时是否存在任何问题或限制?

具体而言、我们想让您谈谈 148.5MHz(或 148.5/REFCLK)输出的抖动性能是否适合满足 1.001MHz 收发器的 REFCLK 要求。

此致、

Conor