主题中讨论的其他器件: LMK04832

工具/软件:

您好、

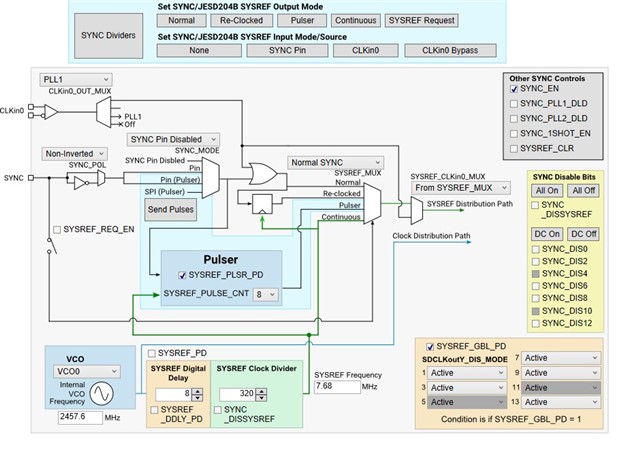

我正在使用 Xilinx ZCU216 (RFSoC) 评估板上的 CLK104 板。 我已经尝试了几天来获取 CLK104 电路板(使用 LMK04828B)、以接受 SMA 连接器上馈送到 CLKIN0 的时钟输入。 无论我怎么做、LMK04828B 都使用连接到 CLKIN1 的板载 10MHz TCXO。 我附加了我在 TICS PRO 中使用的.tcs 文件。

此外、我将 TICS PRO 生成的全部 136 个寄存器写入 LMK04282。 Xilinx 提供的代码 (XRFCLK.c) 仅写入 128 个寄存器。 我认为这是因为有 8 个寄存器是只读的?

谢谢、

Dan

e2e.ti.com/.../245M76_5F00_PL_5F00_122M88_5F00_SYSREF_5F00_7M68_5F00_CLK0.tcs