Other Parts Discussed in Thread: LMK5B12212, LMK5B12212EVM

主题中讨论的其他器件:LMK5B12212、

工具/软件:

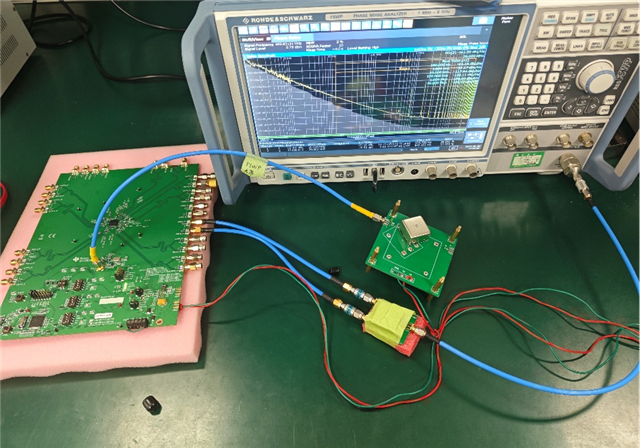

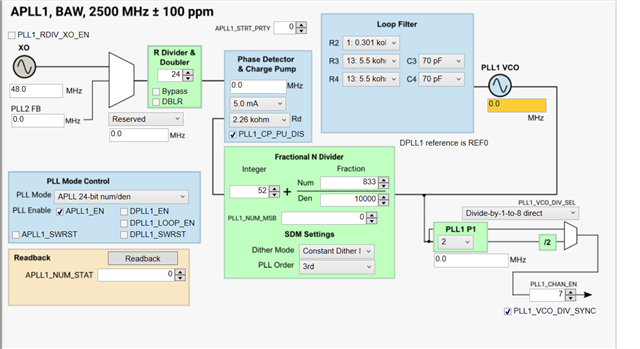

为了评估 lmk5b12212 芯片的抖动性能、使用了官方评估板 LMK5B12212EVM 进行测试。 根据评估板手册中的说明、连接了板载跳线帽和薄代码开关、并连接了 12V 线性电源和 USB 接口。 FSWP 信号源分析仪用于测试相位噪声并计算抖动值。

使用官方 TICS PRO 上部计算机配置输入 XO 频率、输入参考频率(基准是 IN0P 端口上的 10MHz 低相位噪声温控晶体振荡器输入),打开单个差分通道输出,并使用平衡 — 非平衡变压器转换为单端信号用于仪器测试,同时关闭其他通道的输出。

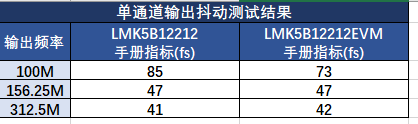

预期的测试结果是评估板手册中给出的测试值:

有关详细信息、请参阅评估板手册的第 33 页。

芯片和评估板中的抖动指示器如下所示:

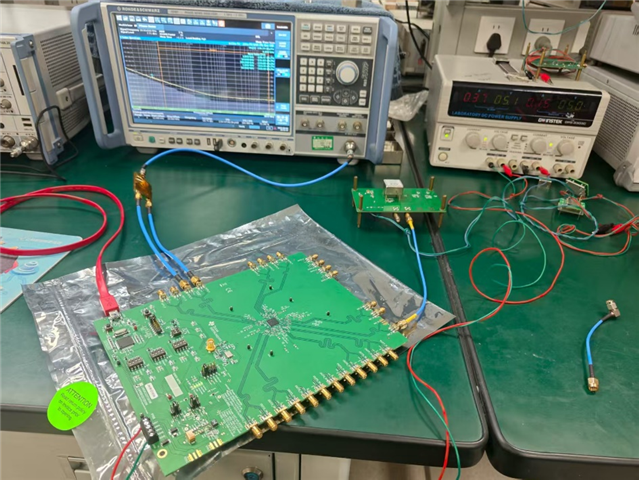

接下来、将使用评估板来测试抖动性能。 以下是测试期间拍摄的真实照片:

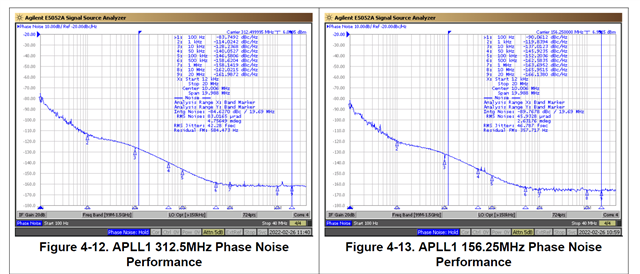

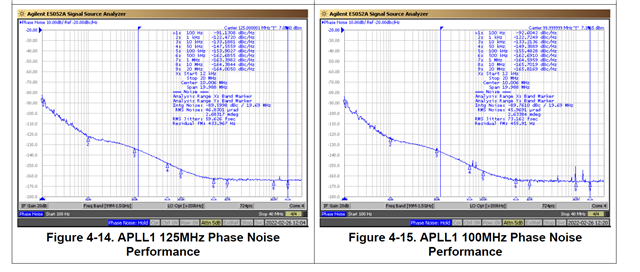

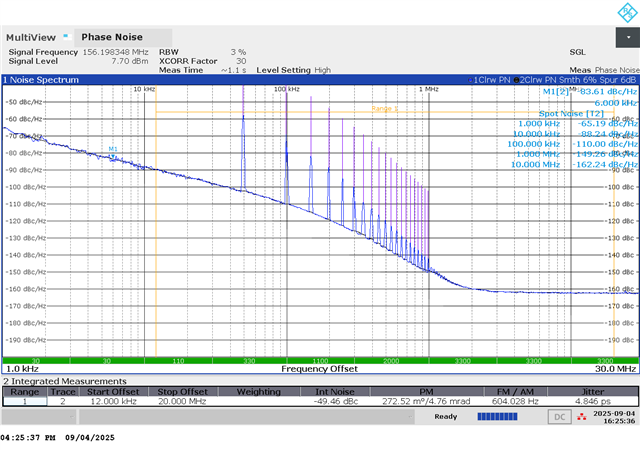

测试发现、如果 DPLL+APLL1 处于打开状态、则输出抖动非常低:

如果 DPLL 关闭且 APLL1 锁定在 XO 上、抖动性能会更好。

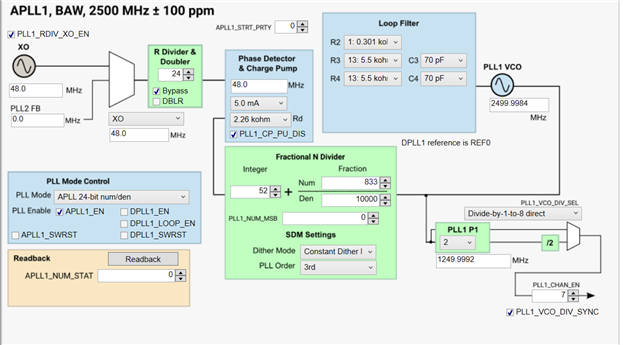

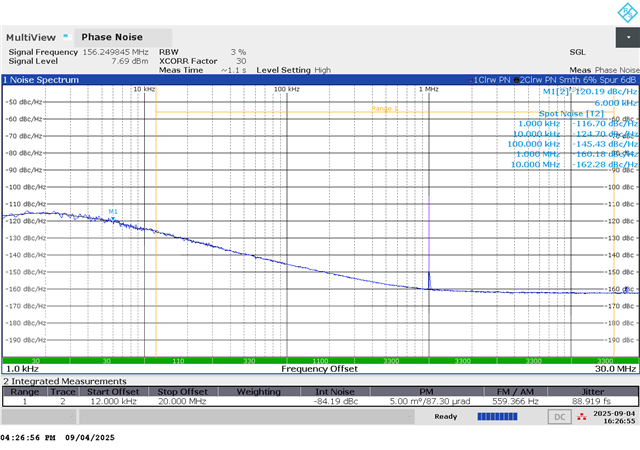

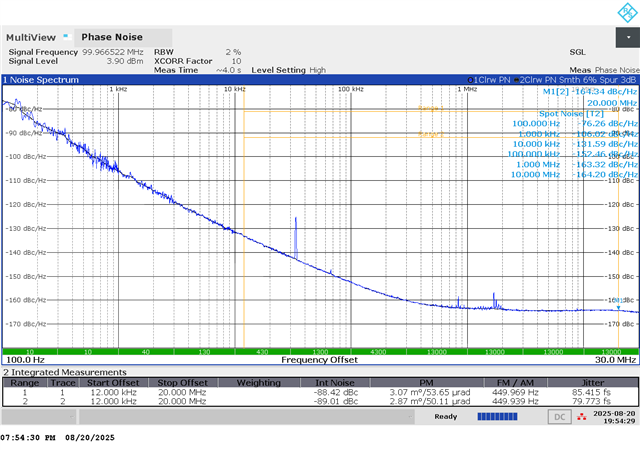

此外、如果 APLL1 的基准输入设置为保留并且 BAW VCO 自由运行、则抖动特性目前性能最佳:

但它仍然远离手册中的指标。

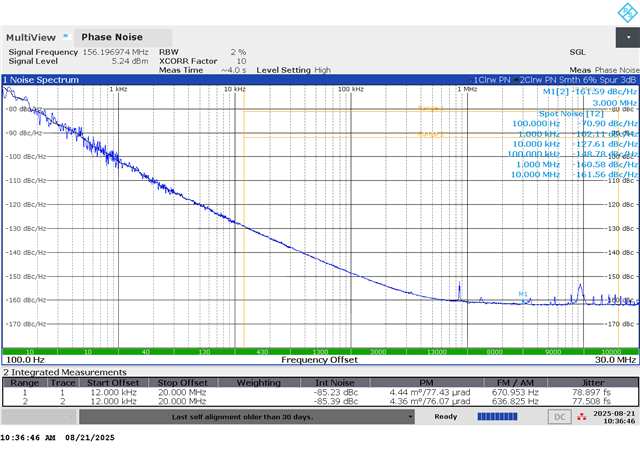

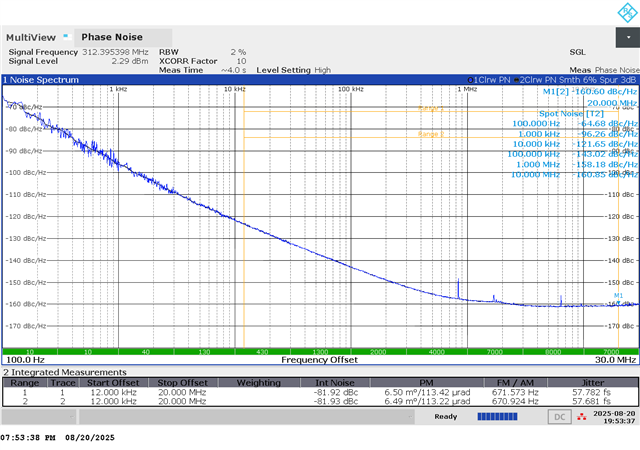

随后、在 100MHz 和 312.5MHz 进行了测试、但抖动性能仍然不足。

此外、将评估板的电源模式更改为 LDO 电源时、发现抖动性能未优化。

我们还尝试使用外部低相位噪声时钟作为 XO 输入来替换板载 48MHz 晶体振荡器、但发现测试结果没有改善。

尝试调整 APLL1 的输出分频系数和通道分频系数、但抖动性能无法满足手动指示器。

总结:通过实际测量、发现手册中给出的抖动指数应参考 BAW VCO 的索引、而使用评估板从测试获得的抖动性能与手册中给出的索引不相符。

请帮助确认原因。 谢谢你