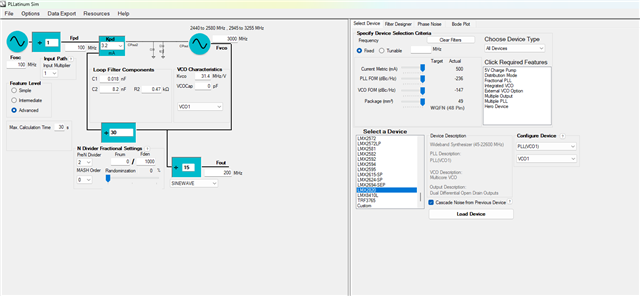

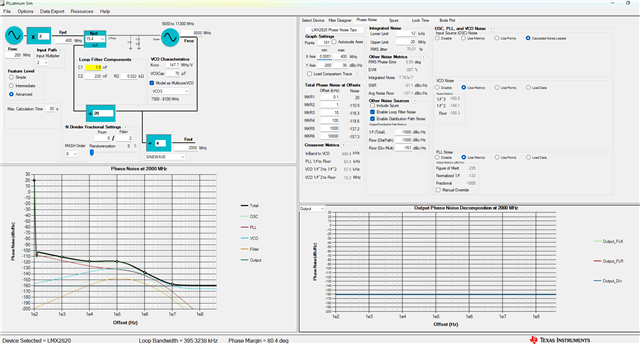

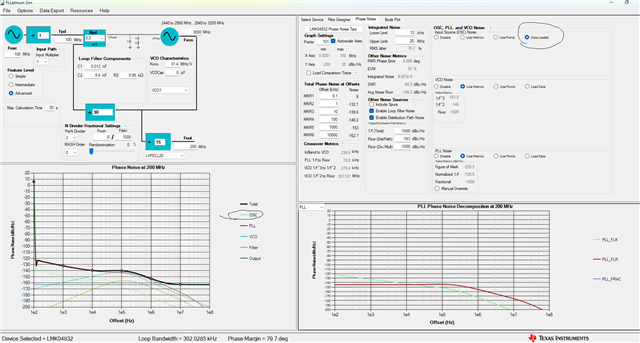

Other Parts Discussed in Thread: LMK04832, LMX2820, LMK61E2

主题中讨论的其他器件: LMX2820、 LMK61E2

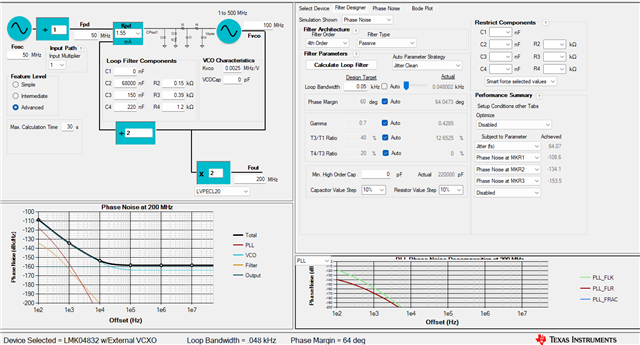

工具/软件:

您好:

我们有一个定制电路板、DAC38 在 8GHz 下运行、ADC12J 在 4G 下运行。它运行稳定。

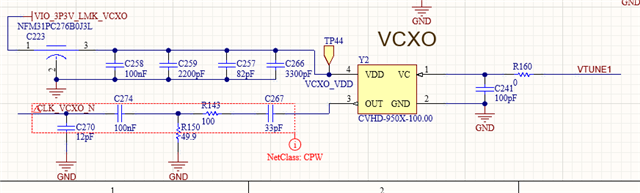

主时钟是一个具有良好规格的 100MHz OCXO。 它还为其他电路板提供与 LMX 位于同一系统中的时钟源。

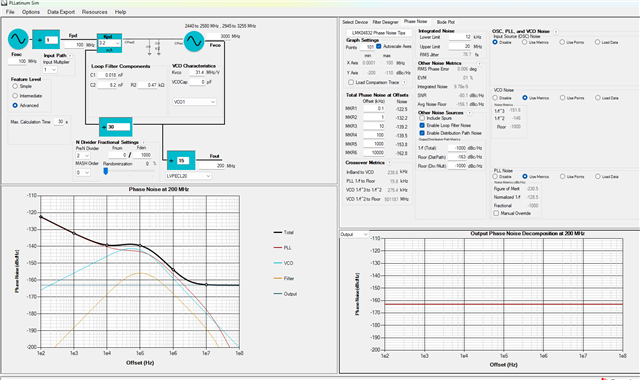

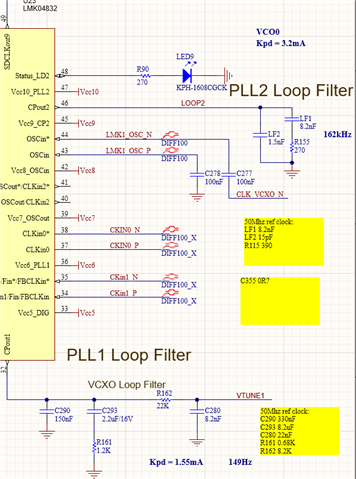

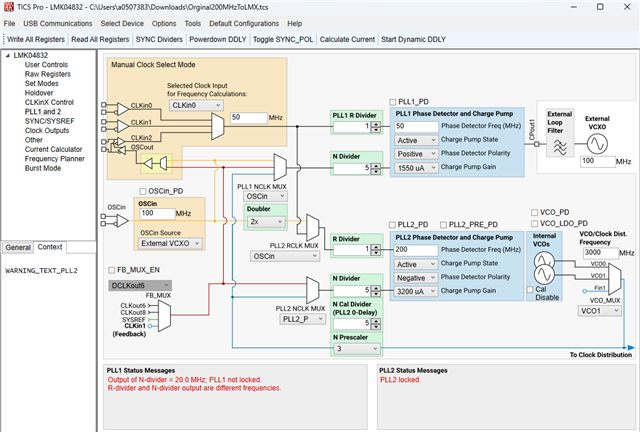

主时钟将 LMK 馈送、LMK 用于生成 SYSREF、125MHz 用于 JESD IP、并将 200MHz 馈送到 LMX。

两个芯片都使用内部 VCO。

现在、我们对 ADC 的 SNR 不满意、我们已经开始研究时钟、我们认为时钟可能具有太多的抖动和可能的低电平(在 BPF 之后只有大约 3.9dBm)。 LMXs RFOUT 的最大输出为 6dBm。

1、因此、我们将 LMK 置于分配模式、使用 SMB100 发生器提供的 1G。 时钟似乎正常、但虽然 DAC 工作、但我们在 ADC 上失去同步。

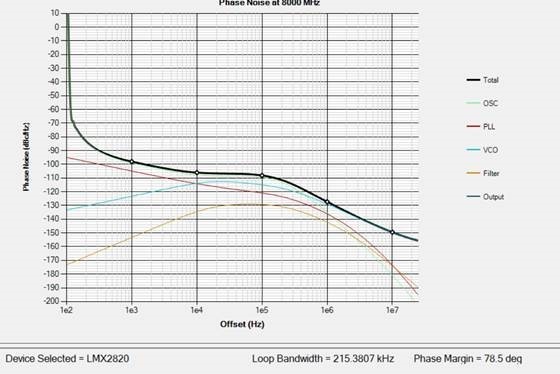

2、然后我们仅更改了 LMX 上的环路滤波器、进行抖动调优(恢复到原始时钟设计)、 也发生了相同的情况。 DAC 仍在运行。

我们无法轻松访问时钟、但我们正在设计几个可以在电路内安装的 PCB、并且我们已经获得了足够快的示波器来进行查看。

但是、您能想到什么会导致上述情况吗? 这是一个精心设计的板、我们已经部署了其中的许多板。

谢谢、

g